解析高速ADC和DAC與FPGA的配合使用

許多數字處理系統都會使用FPGA,原因是FPGA有大量的專用DSP以及block RAM資源,可以用于實現并行和流水線算法。因此,通常情況下,FPGA都要和高性能的ADC和DAC進行接口,比如e2v EV10AQ190低功耗四通道10-bit 1.25 Gsps ADC和EV12DS130A內建4/2:1 MUX的低功耗12-bit 3 Gsps DAC。 通常情況下,這些轉換器的采樣率都達到了GHz的級別。對工程師團隊來說,除了混合信號電路板布局之外,理解和使用這些高性能的設備也是一個挑戰。

本文引用地址:http://www.j9360.com/article/256789.htm這些e2v數據轉換器具有帶寬寬、性能好的特點—數據手冊上通常稱為模擬全功率帶寬—即使是在高奈奎斯特區。(這種能力是不多見的。)正是因為有著優異的轉換性能,才可以使用直接上轉換和下轉換,這樣可以減少部件數量、降低功耗以及節省成本。

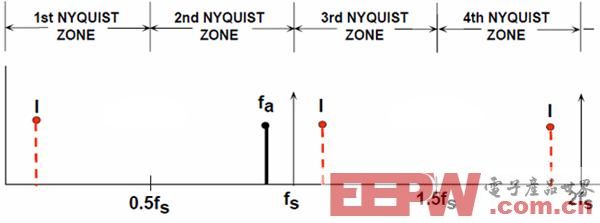

在高頻時,奈奎斯特采樣率(每個周期兩次采樣)是無法維持的。一個例子就是使用一個2.5GHz采樣率的ADC去采樣一個3GHz全功率帶寬的模擬輸入。根據奈奎斯特準則,高于1.25GHz的信號將會被混疊回第一奈奎斯特區,這些混疊圖像是基礎信號的諧波分量,因此和非混疊信號一樣,包含了同樣的信息。

相反的,如果你在使用DAC,進行直接轉換時,你需要確定在上奈奎斯特區你想要使用的諧波。然而,對于DAC,在更高的頻率下,你需要對DAC的衰減進行SINC補償。因此,很常見的是通過仔細選擇輸入組件、阻抗平衡器、交流耦合電容以及通過設計前端模擬預濾波器等等去優化一個ADC或者DAC,使其能在一個奈奎斯特區中工作。

奈奎斯特區和混疊,1、3和4區中顯示的是2區一個信號的鏡像,基礎信號(Fa)和諧波或者諧波含量的鏡像

可以使用下面的算法來確定諧波或者諧波含量合成頻率位置:

Fharm=N ×Ffund

IF (Fharm=Odd Nyquist Zone)

Floc=Fharm Mod Ffund

Else

Floc=Ffund-(Fharm Mod Ffund)

End

這里N是感興趣的諧波的整數。

例如,采樣率為2500MHz,基礎頻率是1807MHz,將會在第一奈奎斯特區有一個693MHz的諧波分量。

前面對頻譜做了一些解釋,另一個重要因素是這些設備和FPGA采用什么方式連接。許多高性能的數據轉換器使用一個工作在較低數據速率的多路復用器來實現轉換器的采樣率-一般都是下圖所示的使用FS/4或者FS/2,圖中顯示的是轉換器的數據流在4條并行的10-bit總線(A, B, C, and D)上的分布:

轉換器的數據流在4條并行的10-bit總線(A, B, C, and D)上的分布

fpga相關文章:fpga是什么

評論