多種EDA工具進行FPGA設計的原理及方法簡介

摘要:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實際操作介紹了整個FPGA的設計流程。

本文引用地址:http://www.j9360.com/article/256057.htm在數字系統設計的今天,片上系統(SoC)技術的出現已經在設計領域引起深刻變革。為適應產品盡快上市的要求,設計者必須合理選擇各EDA廠家提供的加速設計的工具軟件,以使其產品在本領域良性發展。FPGA設計是當前數字系統設計領域中的重要方式之一。本文以多種EDA廠家工具為基礎,系統介紹 FPGA設計的流程。

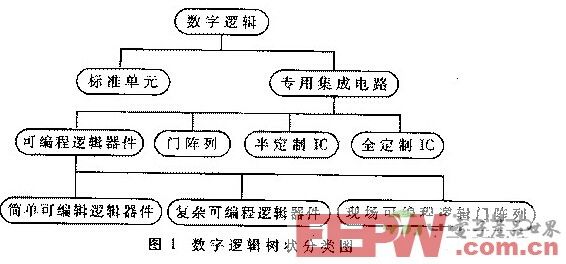

1 數字邏輯劃分與FPGA內部結構

圖1所示為數字邏輯權狀分類圖,由其可以看出,現場可編程門陣列(FPGA)是專用集成電路中可編程邏輯器件的重要分支。

隨著微電子工業的發展與進步,FPGA的集成度已經達到數百萬門,如Xilinx公司的Xcv3200e最大門數為320萬門,Altera公司的 Apex20k1500e為150萬門,且系統時鐘頻率已達到200MHz,支持多種I/I電壓標準,并具有豐富的可重復利用的IP核,便于加速系統設計。

FPGA的內部資源(以Xilinx公司為例)一般分為可編程邏輯塊CLB、輸入輸出塊IOB和可編程連線PI三部分。通過編程控制PI連接各CLB單元,可以形成具有特定功能的電路。使用各公司的專用設計軟件設計FPGA,最終可形成由PI控制CLB單元的位流文件。

Xilinx公司主推的Virtex系列FPGA產品采用0.22微米工藝,具有如下特性:支持9種I/O標準、4個延時鎖定環、塊存儲與分布存儲并存、可編程流水延時存儲、熱控制、配置速率為500Mb/s。而Altera公司的Apex20ke系列同樣是其公司主推的FPGA產品,在內部嘏線資源方面與Xilinx公司產品不同。在Virtex器件中,分為雙長線、單長線、長線幾種,在布線時可以按最近原則進行取舍;而在Apex20ke中,連線僅為一種等長,所以在時序分析時比較準確。

2 FPGA設計流程

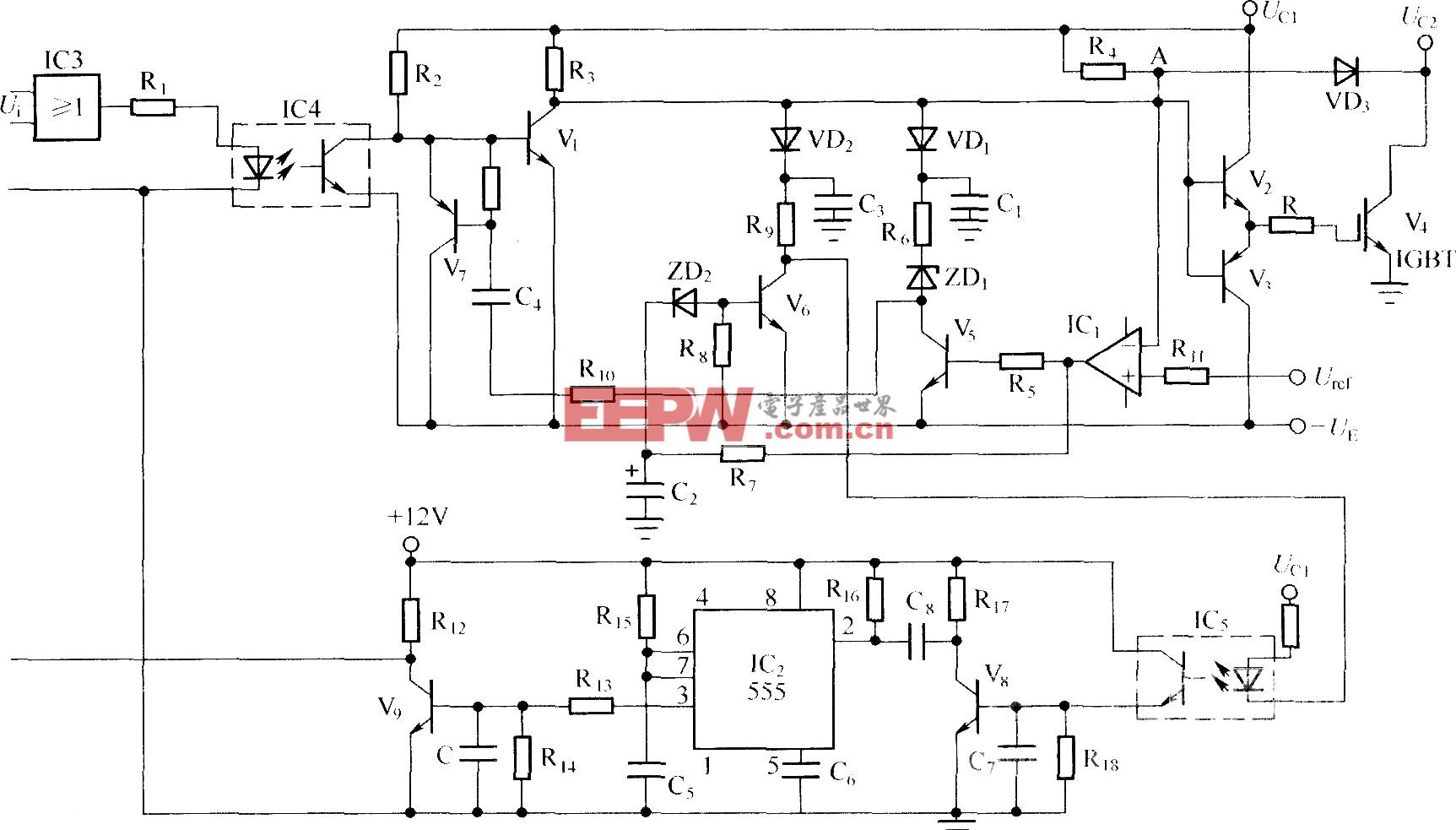

FPGA設計人體分為設計輸入、綜合、功能仿真(前仿真)、實現、時序仿真(后仿真)、配置下載等六個步驟,設計流程如圖2所示。下面分別介紹各個設計步驟。

2.1 設計輸入

設計輸入包括使用硬件描述語言HDL、狀態圖與原理圖輸入三種方式。HDL設計方式是現今設計大規模數字集成電路的良好形式,除IEEE標準中 VHDL與Verilog HDL兩種形式外,尚有各自FPGA廠家推出的專用語言,如Quartus下的AHDL。HDL語言描述在狀態機、控制邏輯、總線功能方面較強,使其描述的電路能特定綜合器(如Synopsys公司的FPGA Compiler II或FPGA Express)作用下以具體硬件單元較好地實現;而原理圖輸入在頂層設計、數據通路邏輯、手工最優化電路等方面具有圖形化強、單元節儉、功能明確等特點,另外,在Altera公司Quartus軟件環境下,可以使用Momory Editor對內部memory進行直接編輯置入數據。常用方式是以HDL語言為主,原理圖為輔,進行混合設計以發揮二者各自特色。

通常,FPGA廠商軟件與第三方軟件設有接口,可以把第三方設計文件導入進行處理。如Quartus與Foundation都可以把EDIF網表作為輸入網表而直接進行布局布線,布局布線后,可再將生成的相應文件交給第三方進行后續處理。

2.2 設計綜合

綜合,就是針對給定的電路實現功能和實現此電路的約束條件,如速度、功耗、成本及電路類型等,通過計算機進行優化處理,獲得一個能滿足上述要求的電路設計方案。也就是是說,被綜合的文件是HDL文件(或相應文件等),綜合的依據是邏輯設計的描述和各種約束條件,綜合的結果則是一個硬件電路的實現方案,該方案必須同時滿足預期的功能和約束條件。對于綜合來說,滿足要求的方案可能有多個,綜合器將產生一個最優的或接近最優的結果。因此,綜合的過程也就是設計目標的優化過程,最后獲得的結構與綜合器的工作性能有關。

FPGA Compiler II是一個完善的FPGA邏輯分析、綜合和優化工具,它從HDL形式未優化的網表中產生優化的網表文件,包括分析、綜合和優化三個步驟。其中,分析是采用 Synopsys標準的HDL語法規則對HDL源文件進行分析并糾正語法錯誤;綜合是以選定的FPGA結構和器件為目標,對HDL和FPGA網表文件進行邏輯綜合;而優化則是根據用戶的設計約束對速度和面積進行邏輯優化,產生一個優化的FPGA網表文件,以供FPGA布局和布線工具使用,即將電路優化于特定廠家器件庫,獨立于硅持性,但可以被約束條件所驅動。

利用FPGA Compiler II進行設計綜合時,應在當前Project下導入設計源文件,自動進行語法分析,在語法無誤并確定綜合方式、目標器件、綜合強度、多層保持選擇、優化目標等設置后,即可進行綜合與優化。在此可以將兩步獨立進行,在兩步之間進行約束指定,如時鐘的確定、通路與端口的延時、模塊的算子共享、寄存器的扇出等。如果設計模型較大,可以采用層次化方式進行綜合,先綜合下級模塊,后綜合上級模塊。在進行上級模塊綜合埋設置下級模塊為Don't Touch,使設計與綜合過程合理化。綜合后形成的網表可以以EDIF格式輸出,也可以以VHDL或Verilog HDL格式輸出,將其導入FPGA設計廠商提供的可支持第三方設計輸入的專用軟件中,就可進行后續的FPGA芯片的實現。綜合完成后可以輸出報告文件,列出綜合狀態與綜合結果,如資源使用情況、綜合后層次信息等。

2.3 仿真驗證

從廣義上講,設計驗證包括功能與時序仿真和電路驗證。仿真是指使用設計軟件包對已實現的設計進行完整測試,模擬實際物理環境下的工作情況。前仿真是指僅對邏輯功能進行測試模擬,以了解其實現的功能否滿足原設計的要求,仿真過程沒有加入時序信息,不涉及具體器件的硬件特性,如延時特性;而在布局布線后,提取有關的器件延遲、連線延時等時序參數,并在此基礎上進行的仿真稱為后仿真,它是接近真實器件運行的仿真。

2.4 設計實現

實現可理解為利用實現工具把邏輯映射到目標器件結構的資源中,決定邏輯的最佳布局,選擇邏輯與輸入輸出功能連接的布線通道進行連線,并產生相應文件(如配置文件與相關報告)。通常可分為如下五個步驟。

fpga相關文章:fpga是什么

評論