基于Nios II的AT24C02接口電路設計與實現

0 引 言

本文引用地址:http://www.j9360.com/article/248950.htm在實際的應用中,為了保護現場,經常需要將系統斷電之前的工作狀態與重要運行數據保存在非易失存貯器中,以便在下次開機時,能恢復到原來的工作狀態。針對這種保存的數據量不大和存儲速度要求不高的特點,可采用“NiosⅡ+AT24C02"設計方案進行設計。本文在討論了I2C通信協議的基礎上,利用FPGA技術,設計了NiosⅡ與AT24C02”之間進行通信的接口電路。本接口電路能產生基于I2C通信協議的讀寫操作時序,成功實現了對AT24C02的讀寫功能。由于所有的時序,都是由硬件產生,因此,本設計具有控制簡單、成本低廉等特點。

1 AT24C02A芯片簡介

AT24C02A芯片,是由ATMEL公司生產的基于I2C總線型的串行電可擦除的可編程存儲器(EEPROM),內部含有2Kbit的存儲單元,是通過二根線(SDL與SCL)與外部I2C控制器交換數據。

AT24C02A芯片的主要特性如下:

低電壓和標準電壓操作

-2.7(VCC=2.7V至5.5V)

-1.8(VCC=1.8V至5.5V)

片內存儲容量為256×8 bit(2K)

2線串行接口

施密特觸發器,過濾輸入的噪聲抑制

雙向數據傳輸協議

100 kHz(1.8V、2.5V、2.7V)和400 kHz(5V)兼容性

寫保護引腳的硬件數據保護。

2 I2C通信協議

2.1 I2C通信協議簡介

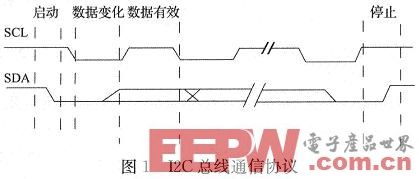

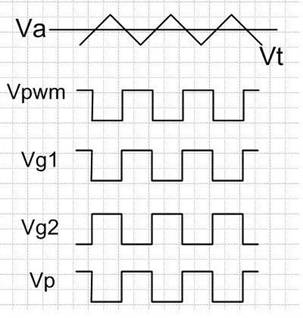

AT24C02A器件采用成本低廉的I2C(Inter integrat-ed Circuit)總線通信協議,即利用串行數據線(SDA)和串行時鐘線(SCL)成功實現了主模塊與從模塊之間數據通信,圖1為I2C通信協議的時序圖。由圖可知,完成一次數據的傳輸必須要經歷啟動、數據傳輸與停止三個基本的過程:當串行時鐘線(SCL)為高電平時,串行數據線(SDA)從高電平變成低電平,“啟動”I2C通信;當串行時鐘線(SCL)為高電平時,串行數據線(SDA)從低電平變成高電平,“停止”I2C通信;在數據的傳輸過程中,串行數據線(SDA)上的數據的改變,只能在串行時鐘線(SCL)為低電平期間完成。

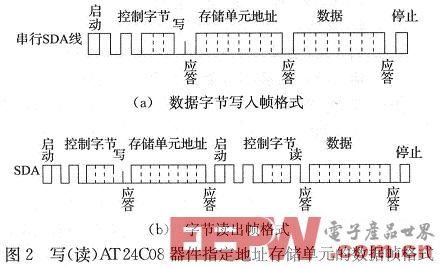

2.2 AT24C02A器件讀寫時序

圖2為寫(讀)AT24C02A器件中指定地址存儲單元的數據幀格式,圖2(a)為寫操作的幀格式,(b)為讀操作幀格式。要想把一個字節數據發送到器件中(或從器件中讀取一個字節數據)除了給出具體的地址信息之外,還要給出該器件的控制信息:首先由控制器發出“啟動”信號,啟動I2C總線的通信,然后發送一個控制字節,前7位為器件的片選地址,最后1位為讀寫控制位,“0”表示寫,“1”表示讀。當傳完控制字節之后,掛在I2C總線的所有的器件比較控制字節片選地址(前7位)是否與自已的物理地址一致,如一致,則發一個應答信號。控制器接收到應答信號之后,再發器件內部存儲單元地址和其他的信息。

3 AT24C02A讀寫控制接口設計

3.1 寄存器組定義

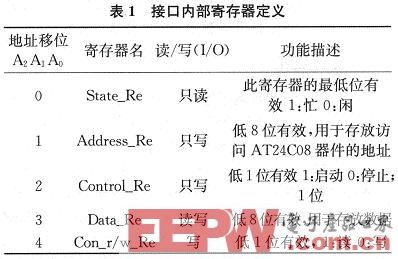

為了實現NiosⅡI能與外部設備進行交換數據,首先要在AT24C08讀寫控制接口中定義寄存器,包括數據寄存器、狀態寄存器和控制寄存器。表4-1AT24C02A讀寫控制器內部寄存器定義的情況:State_Re為此接口電路的狀態寄存器,最低位有效,用來表示接口電路的狀態,“1”表示接口處于“忙”狀態中,此時表示接口正處于讀寫外部設備(AT24C02A)中,不能對此控制接口進行操作,只到接口處于“0”狀態時為止;Address_Re為數據寄存器,用于存放NiosⅡ要訪問AT24C02A器件內部單元的地址數據;Control_Re為控制寄存器,控制著接口電路啟動或停止,“1”為啟動,“0”停止;Data_Re為數據寄存器,用于存放傳輸的數據;Con_r/w_Re為控制寄存器,控制數據的傳輸方向,高電平為讀(輸入),低電平為寫(輸出)。

3.2 邏輯功能模塊設計

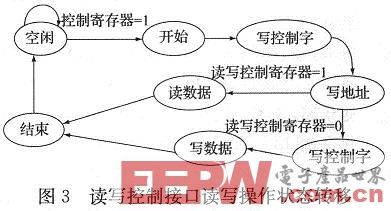

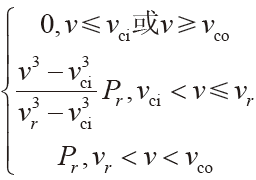

在接口電路中,除了定義接口電路的寄存器組之外,還要利用硬件描述語言來描述接口電路要實現的功能,即邏輯功能模塊的設計。接口電路要完成的主要功能是,用接口電路產生如圖3所示的時序,成功讀寫外部存儲器件。在本設計中,采用了有限狀態機來實現這一功能,圖3為本設計的各個狀態之間轉換狀態圖:當NiosⅡ要交換數據時,首先要讀State_Re的值,并判定電路是否為“空閑”狀態,只有狀態機處在空閑狀態,才允許進行一次讀寫操作,并修改狀態寄存器的值為“忙”狀態;當完成一次讀寫操作時,修改狀態寄存器的值為“閑”狀態。

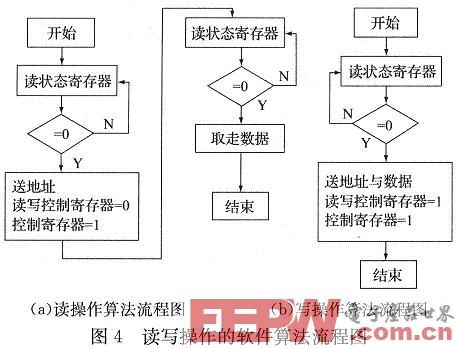

4 在NiosⅡIDE環境中軟件設計

打開NiosⅡEDS,并點擊new菜單建立工程文件,在IDE環境中完成接口電路驅動程序編寫。驅動程序主要的任務,是判斷接口電路所處的狀態,當接口電路處于“閑”狀態時,設置好接口電路中的寄存器中的值,并啟動一次讀寫操作。圖4為驅動程序的算法流程圖。

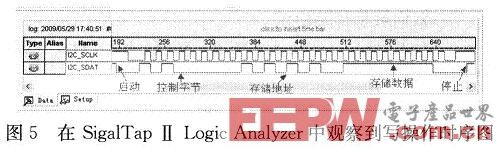

5 測試結果

為了驗證設計的正確性,對以上設計進行測試。在測試的過程中,可以利用嵌入式邏輯分析儀 (SigalTapⅡLogic Analyzer)來分析信號時序,打開工程文件,點擊File菜單,為本設計新建一個矢量波形文件(Vectorwaveform File),把要測試的信號添加到此文件中來,并設置好相關參數,保存并編譯系統,然后把系統的配制文件下載到EP1C6Q240C8可編程器件中等待調試,最后,在:NiosⅡ的ID E中,把驅動程序下載到可編程器件中,并在QuartusⅡ軟件中打開矢量波形文件,觀察被測信號的時序,圖5為接口電路把數據為“11111111”寫到地址為“10101010”單元中的時序圖。從圖可以看出,啟動時序、數據傳輸時序和停止時序都滿足I2C通信協議要求,驗證了本接口電路的正確性。

6 結束語

本文在討論了I2C通信協議的基礎上,重點介紹了AT24C02A讀寫接口電路設計方法,包括接口電路的寄存器定義、邏輯功能模塊設計和驅動程序的編寫,并利用嵌入式邏輯分析儀(SigalTapⅡLogic Analyzer)對本接口電路進行測試,測試結果表明,本設計滿足設計要求,并在實際電路中得到應用。

施密特觸發器相關文章:施密特觸發器原理

評論