基于FPGA的超聲電機驅動控制電路

摘要:針對直線超聲電機的特點,設計了一種以FPGA為核心、基于SOPC技術和NiosⅡ軟核處理器的新型超聲電機驅動控制器,以控制直線型超聲電機的速度和位移。該驅動控制器把CPU、DDS模塊以及光柵反饋計數模塊都集成在一片FPGA中,具有電子元件使用少,功耗低,易修改、易升級等特點,為超聲電機的各種運動平臺提供了一個良好的閉環控制系統。

本文引用地址:http://www.j9360.com/article/247593.htm超聲電機是一種新型微特電機,其工作原理是通過壓電材料的逆壓電效應,使定子在超聲頻段微幅振動,依靠摩擦將振動轉換成動子的旋轉(直線)運動。超聲電機具有體積小,重量輕、結構緊湊、響應快、無電磁干擾等優點,在航天宇航和軍事裝備等領域有著廣泛的應用前景。

近些年來,我國在超聲電機控制方面,提出了一些控制理論,并搭建了一些用于超聲電機驅動的實際驅動與控制電路。2010年,薛雯玉碩士研究了基于DSP芯片的超聲電機驅動控制器,但驅動電路仍以傳統的模擬電路為主,精度不高,不能實時的調頻、調相。2011年,孫霖碩士研究了基于DSP/FPGA的超聲電機驅動控制器,利用DDS技術產生數字正弦波,雖然提高了精確度和實時性,但是浪費了很多芯片的邏輯資源,也不利于驅動控制電路的小型化。

本文使用Altera公司的EP3C400240C8芯片設計了一種以FPGA為核心、基于SOPC技術和NiosⅡ軟核處理器的新型超聲電機驅動控制器。在FPGA內部用SOPC(可編程片上系統)的思想定制了一個NiosⅡ軟核處理器作為控制運算部分,用Verilog語言編寫出了頻率、相位、幅度都可調的DDS模塊和光柵反饋計數模塊,這樣的一個閉環系統在滿足控制精度和實時性的同時具有良好的靈活性和可重構性,并且做到了以極少的硬件資源和高度集成的系統結構去控制超聲電機運行,便于驅動控制電路的小型化。

1 驅動控制器的設計

1.1 驅動控制電路

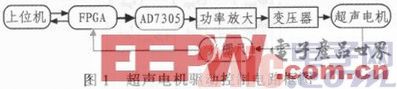

本文提出的超聲電機驅動控制系統由控制驅動器和功放/升壓電路組成。圖1是以FPGA為核心構建的超聲電機驅動控制電路。超聲電機的驅動機理要求驅動器必須提供在超聲頻段內兩相具有一定相位差的同頻、等幅正弦交流電,電壓在幾十伏到幾百伏之間。該電路的功能全部由FPGA的軟件實現,控制和輸出正弦交流電,大大提高了控制系統的穩定性和精確性,并使控制系統電路板的面積大幅度縮小,一塊控制板可以同時控制數個超聲電機。

此驅動控制系統用FPGA內部編寫的DDS模塊輸出兩路具有一定相位差的正弦波數據,然后通過DA芯片轉成正弦波信號,經過功率放大之后,最后用變壓器抬高電壓。

該電路加載超聲電機后輸出的波形如圖2所示,波形變的光滑很多。當超聲電機在運行過程中發生頻率漂移的情況時,系統也能夠從速度的改變量來調整相應的驅動輸出,不會出現電機速度不穩定的現象。

1.2 FPGA內部系統

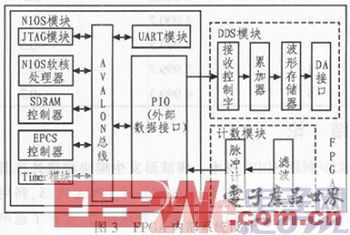

圖3是超聲電機控制驅動電路中FPGA內部的構架。其設計的核心是可裁剪的Nios II軟核和發出正弦信號的DDS模塊以及讀取光柵編碼器反饋脈沖的計數模塊。

1.2.1 NiosⅡ系統的搭建

Nios II是Altera公司開發的軟核32位的RISC微處器,作為一個采用硬件描述語言編寫的軟核,Nios II可以通過內帶的Avalon總線機制與其他采用HDL語言描述的硬件接口模塊組成Nios系統一起嵌入到Altera的Stratix、Cyclone或APEX系列的FPGA中,從而構成一個可編程片上系統設計。

首先要構建一個基于Nios II的最小系統,這個系統的組件都在SOPC Builder提供的IP核中,依次選擇Nios II處理器、EPCS控制器、SDR AM控制器、JTAG模塊。其中,NiosⅡ實現MCU的功能,SDRAM和EPCS控制器組件用來連接外部存儲器,JTAG模塊實現程序的調試與下載。除此以外,我們還需要用到串口接收上位機發送來的數據以及定時器中斷,因此在系統中添加UART模塊和定時器模塊。最后,處理器要控制DDS模塊的運行并且接收光柵計數模塊計算出的脈沖數,還需要添加一些I/O口用作數據的傳輸。這樣,FPGA內部的一個NIOS系統就構建完成了。

1.2.2 DDS模塊

直接數字頻率合成器(Direct Digital Frequency Synthesizer)是一種基于全數字技術,從相位概念出發直接合成所需波形的一種頻率合成技術。基本原理是以數控振蕩器的方式,產生頻率、相位可控制的正弦波、余弦波、三角波、三角波、方波等波形。圖4所示為DDS的基本結構。

圖4中,fc為時鐘頻率,K為頻率控制字,N為相位累加器的字長,D為ROM數據線寬度。

本文的DDS設計主要分為3個模塊:控制字接收模塊,用來與NIOS系統進行通信,接收來自上位機的控制字;波形存儲器模塊,用來產生驅動信號所需要的波形,本文只需要產生正弦波;相位累加器模塊,用來產生頻率和相位,本文是將接收到的頻率和相位控制字轉化為實際的頻率和相位。

1.2.3 脈沖計數模塊

脈沖計數模塊由濾波和計數兩部分構成,主要是為了讀取光柵編碼器反饋回來的信息,從而實現對電機的精確定位和速度控制。本文使用的光柵編碼器,其分辨率為0.5um/count,輸出A+/A-、B+/B- 2路差分信號,為將編碼器的差分輸出轉換成單端脈沖信號,本文選用了26LS32AC差分轉單端芯片實現差分信號的轉換。轉換后的兩路信號A、B是一組正交脈沖信號,電機朝不同方向運動時,A、B兩路信號之間

fpga相關文章:fpga是什么

脈沖點火器相關文章:脈沖點火器原理

評論