一種基于FPGA的視頻邊緣檢測系統設計

摘要:對于視頻圖像檢測與識別的需要,提出了一種基于FPGA的視頻邊緣檢測系統設計方案,并完成系統的硬件設計。通過FPGA控制攝像頭進行視頻采集,雙端口SDRAM對圖像數據進行緩存,FPGA再對數據進行實時處理。實際采用DE2-115開發板和CMOS攝像頭OV7670為硬件平臺進行驗證。結果表明,該系統具有實時性高,檢測準確的特點,達到了設計要求。

本文引用地址:http://www.j9360.com/article/246281.htm隨著科技的發展,視頻采集系統越來越廣泛的應用于各個領域,如體育直播,視頻會議,導彈的電視制導等等。而圖像邊緣是圖像的基本特征之一,其中包含了很重要的邊界信息,這些信息是圖像分析、目標識別的基礎。在交通信息控制應用領域中,邊緣檢測已經是車牌識別、車流量監控、自動導航等技術中的重要環節。通過有效的邊緣檢測,可以大大簡化后續圖像處理過程對圖像信息的分析工作。對于視頻圖像的邊緣檢測,若采用軟件方式實現由于受到系統處理速度的限制,容易出現斷幀現象,這對于要求實時處理的情況下將是一個很大的缺陷。硬件實現主要有基于專用芯片,基于DSP和基于FPGA的3種處理方式。基于專用芯片方式并不適合前期產品的開發。基于DSP方式在運算速度、數據吞吐量等方面有限制。本設計基于FPGA實現,邊緣檢測采用流水線結構。實驗結果表明,該系統十分適合視頻數據的處理。

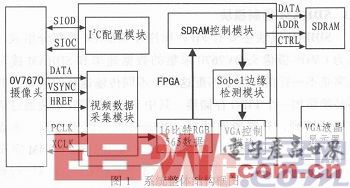

1 系統總體設計

本系統基于一片Altera公司的Cyclone IV系列的EP4CE115F29CN7主控FPGA,系統的整體結構框圖如圖1所示。主要包括:攝像頭I2C配置模塊、視頻數據采集模塊、SDRAM控制模塊、Sobel邊緣檢測模塊和VGA控制模塊。FPGA首先通過I2C總線完成對OV7670的初始化,然后將采集到的數據通過視頻數據采集模塊轉換成RGB565標準的視頻數據,圖像數據通過FIFO_IN模塊在SDRAM中進行緩沖,Sobel邊緣檢測模塊通過FIFO _OUT模塊讀取數據并進行處理,VGA控制模塊控制VGA接口的行同步和場同步信號完成VGA顯示。

2 視頻采集與邊緣檢測子模塊

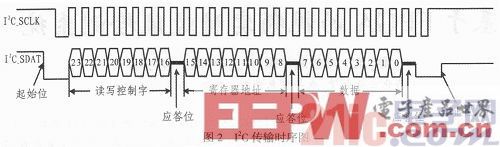

2.1 I2C配置模塊

本系統采用OmniVision公司的OV7670這一款CMOS傳感器,為系統提供視頻信號。通過SCCB(Serial Camera Control Bus)總線對OV7670的共201個控制寄存器進行配置,來改變輸出數據的格式、視頻分辨率、傳輸方式,調整圖像的白平衡、飽和度、色度、伽瑪曲線等。兩線制的SCCB總線與I2C總線相同,都是雙向兩線制同步串行總線。I2C傳輸時序如圖2所示,I2C_SCLK就等同于SCCB中的SIOC、I2C_SDAT就等同于SC CB中的SIOD,模塊每次傳輸24位數據,前8位為從設備地址(0x42代表寫寄存器,0x43代表度寄存器),中間8位是從設備寄存器地址,最后8位是對寄存器進行配置的數據。

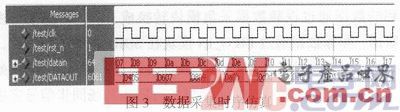

2.2 視頻數據采集模塊

視頻數據采集模塊,主要是通過FPGA配合CMOS攝像頭OV7670的行、場同步信號采集圖像數據。首先通過配置控制寄存器,控制OV7670輸出視頻數據為RGB565格式。因為OV7670數據位寬為8,視頻數據采集模塊主要是將采集到的前后2個8位數據合并成一個16位數據,以方便數據在SDRAM中的緩存以及后續模塊的處理。如圖3所示為數據采集ModelSim時序仿真圖。

2.3 SDRAM控制模塊

SDRAM模塊主要有FIFO和片外SDRAM兩部分組成,因為CMOS攝像頭OV7670采集的數據速率和SDRAM讀寫速率是不一樣的,為了匹配這兩個不同傳輸速率的模塊,其中必須添加一個FIFO存儲器。其中FIFO不需要單獨通過語言描述得到,只需要通過MegaWizard工具配置得到。本設計中用到的SDRAM為DE2-115開發板上的兩個64M字節SDRAM,其中每個SDRAM又包含4個BANK。SDRAM行地址線和列地址線是復用13位的地址總線,在讀寫時,先要激活某個BANK,接著鎖存行地址,最后在讀寫指令有效時鎖存列地址。SDRAM的最高讀寫速率可達到166 MHz,本系統中應用為100 MHz,同時每個時鐘上升沿又可讀寫16 bit數據,因此SDRAM完全可以實現數據的無縫緩沖工作。

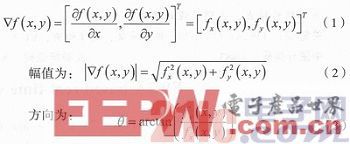

2.4 Sobel邊緣檢測模塊

圖像邊緣是一幅圖像中灰度變化比較劇烈的區域,計算灰度圖像中各區域的梯度幅值可以用來判定圖像的邊緣信息。設圖像的亮度為f(x,y),則梯度可以定義如下:

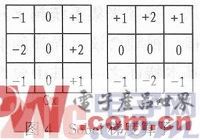

Sobel邊緣檢測便是是基于梯度的檢測,其利用Sobel算子如圖4所示Gx與Gy,在3×3的圖像鄰域內和亮度數據做卷積運算,表達式如下:

用硬件左邊緣檢測,由于是實時處理,SDRAM中緩存的數據只是連續視頻圖像中一幀圖像,而且視頻數據還不停的從攝像頭中傳過來,因此就不能像軟件處理那樣先建立一個二維的數據陣列,這樣就必須采用流水線方式進行運算,流水線數目和每次參加運算的像素數目相等,這里就總共需要9條流水線。為此我們就專門設計了3條Line_Buffer來完成式(4)與式(5)的運算,3條Line_Buffer由MegaWizard中配置的alts hift_tab完成,altshift_tab實際上就是一個移位寄存器,因為視頻分辨率為640×480像素,所以每條Line_Buffer實際是向后移位一整行,也就是640個像素值。這樣就等同于3條Line_Buffer中的數據視頻圖像中相毗鄰的三行圖像數據,這3行數據再與Sobel算子做卷積。如圖5所示為卷積運算硬件結構圖,其中P9—P1為像素數據,X9--X1為Sobel梯度算子。乘法與并行加法部分分別有MegaWizard配置的altmult_add和parallel_add完成。

fpga相關文章:fpga是什么

攝像頭相關文章:攝像頭原理

評論