TMS320C6701控制多片AD9852的接口

1 AD9852和TMS320C6701簡介

該系統選用的直接頻率合成器是AD公司生產的AD9852,它能產生頻率、相位、幅度可編程控制的高穩定的模擬信號。在最高系統時鐘300MHz時,輸出頻率的范圍可達DC-120MHz,精度可達1.066μHz,頻率轉換速度可達每秒1×10 8個頻率點;具有14位數控調相和12位數控調幅功能;具有相移鍵控(PSK)、掃頻功能(CHIRP)和頻移鍵控(FSK)功能。

該系統選用的數字信號處理芯片(DSP)是TI公司生產的高速浮點TMS320C6701,其內部CPU集成了8個并行功能單元,配有32個32位通用寄存器,它在6ns周期時間里最多可同時執行8條32位指令,其運算能力可達1G FLOPS;存儲器尋址空間為32位,可尋址8/16/32位數據;有4個自加載的DMA傳輸通道。

2 TMS320C6701與AD9852接口電路

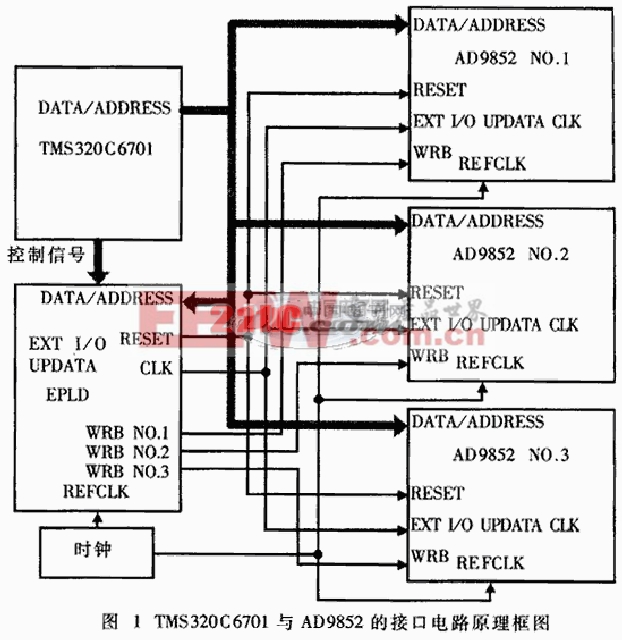

TMS320C6701是本系統的控制中心,其主要功能是將控制信號和信號波形參數發送到AD9852內部相應的控制寄存器,二者的接口電路原理框圖如圖1所示。

對AD9852內部控制寄存器可以進行并口或串口的讀寫操作。因為AD9852的串口傳輸速率最大僅為10MHz,而并口傳輸速率可達高達100MHz,為了提高DSP對AD9852的控制速度,本系統采用了并行接口方式,三片AD9852的8位數據總線同時占用DSP數據總線的D0~D7位,它們的6位地址總線同時點用DSP地址總線的A2~A7位。由于AD9852器件沒有片選輸入信號。需要利用DSP的寫信號/AWR、片選信號/CE0和高位地址數據線的第A21~A20位,并由EPLD對其進行譯碼要成WRB NO.1、WRB NO.2和WRB NO.3寫信號,分別控制三片AD9852器件的寫信號WRB,該寫信號負責把數據總線上的數據寫入到AD9852的I/O緩沖寄存器中數據總線上數據寫入到AD9852的I/O緩沖寄存器中進行緩存,這樣就實現了片選不同AD9852芯片目的。

TMS320C6701還控制EPLD產生三片AD9852需要的復位信號RESET和外部更新時鐘EXT I/O UPDATECLK。為了使三片AD9852和EPLD之間系統時鐘同步,它們的外部參考時鐘REFCLK由同一個50MHz的溫補晶振提供。[next]

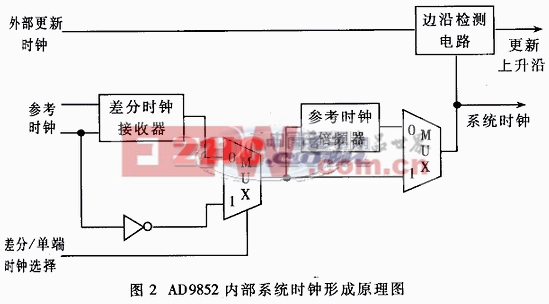

3.1 參考時鐘信號

3.2 更新時鐘信號

在同時定改三片AD9852內部的頻率和相痊控制寄存器的過程中,為了防止因數據建立和保持時間的原因而出現編程信息傳輸錯亂,使AD9852的輸出信號失去同步,本系統使用由EPLD提供的同一個外部更新時鐘信號。若使用AD9852內部更新模式,盡管可以簡化系統設計,但因為AD9852內部時鐘頻率較高,會受到AD8952接口速率的限制,使AD9852的控制時序不易控制。對外部更新時鐘信號的PCB布線同參考時鐘的要求一樣,必須使它的上升沿同時到達每片AD9852.

3.3 復位信號

3.4 參考時鐘信號倍頻

3.5 數據總線和地址總線信號

4 AD9852的操作控制時序

(1)給系統上電,DSP控制EPLD產生復位信號RESET,此信號需要至少保持10個參考時鐘周期的高電平;

(2)依次給每個AD9852發送控制字,使每個AD9852工作狀態由缺省的內部更新時鐘模式改變成外部時鐘更新模式;

(3)將AD9852時鐘倍頻器工作的控制字依次寫入每個AD9852的I/O緩沖寄存器中,EPLD產生外部更新時鐘的同時更新每個AD9852內部控制寄存器;

(4)至少等待1.0ms時間使AD9852內部鎖相環鎖定。內部鎖相環鎖定后,DSP就可以發送有關信號波形參數給每片AD9852,對它們的內部控制寄存器內容進行同步更新,使三片AD9852輸出同步的模擬信號。

采用DSP控制DDS的方法完成的雷達信號模擬器已經得到了應用,結果證該模擬器輸出的三路信號波形同步,具有很高的距離和速度分辨率。另外,DDS技術具有的靈活可編程特性使得上述結構的模擬器還可以有其它應用,只要改變DSP控制程序,就可以根據需要產生三路同步的各種信號波形。

評論