以太網控制器ENC28J60及其接口技術

引言

ENC28J60是Microchip Technology(美國微芯科技公司)近期推出的28引腳獨立以太網控制器。

在此之前,嵌入式系統開發可選的獨立以太網控制器都是為個人計算機系統設計的,如RTL8019、AX88796L、DM9008、CS8900A、LAN91C111等。這些器件不僅結構復雜,體積龐大,且比較昂貴。目前市場上大部分以太網控制器的封裝均超過80引腳,而符合IEEE 802.3協議的ENC28J60只有28引腳,既能提供相應的功能,又可以大大簡化相關設計,減小空間。

1 結構和功能

采用業界標準串行外設接口(SPI)的以太網控制器ENC28J60具有以下主要特征:

◆ 符合IEEE 802.3協議。內置10 Mbps以太網物理層器件(PHY)及媒體訪問控制器(MAC),可按業界標準的以太網協議可靠地收發信息包數據。

◆ 具有可編程過濾功能。特殊的過濾器,包括Microchip的可編程模式匹配過濾器,可自動評價、接收或拒收Magic PACket,單播(UNIcast)、多播(Multicast)或廣播(Broadcast)信息包,以減輕主控單片機的處理負荷。

◆ 10 Mbps SPI接口。業界標準的串行通信端口,使得低至18引腳的8位單片機也具有網絡連接功能。

◆ 可編程8 KB雙端口SRAM緩沖器。以高效的方式進行信息包的存儲、檢索和修改,以減輕主控單片機的內存負荷。該緩沖存儲器提供了靈活可靠的數據管理機制。

2 硬件設計

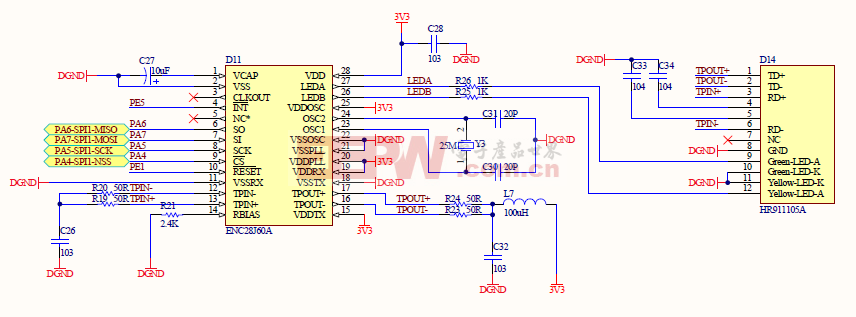

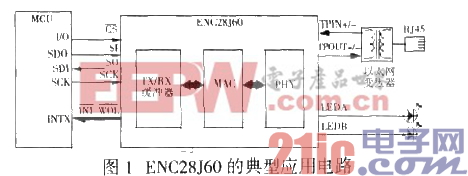

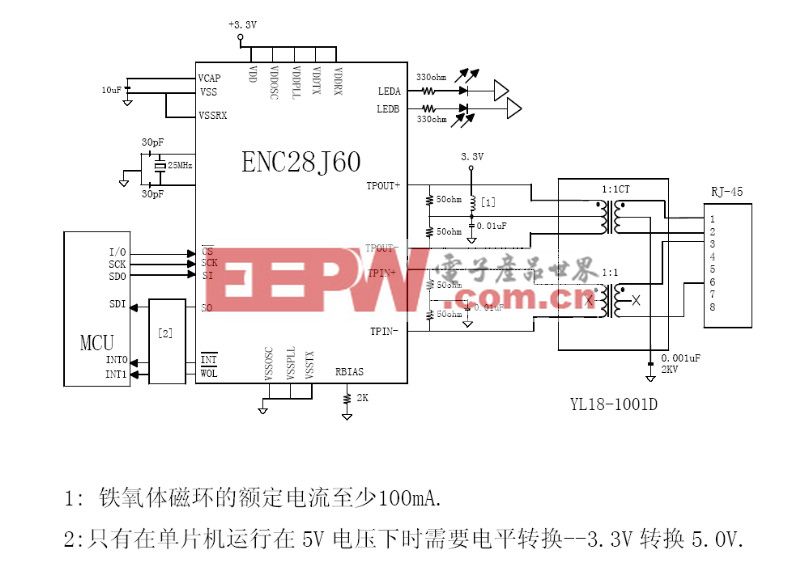

ENC28J60的硬件設計需要注意復位電路,時鐘振蕩器,振蕩器啟動定時器,時鐘輸出引腳,變壓器、終端和其他外部器件,輸入/輸出電平等幾個方面。(圖1可供參考)

2.1 復位電路

ENC28J60有上電復位(Power-on Reset)功能,RESET引腳上的低電平使ENC28J60進入復位模式;RESET引腳內部有弱上拉電阻。ENC28J60的硬件連接如圖1所示。

2.2 時鐘振蕩器

ENC28J60需要一個25 MHz的晶振,接在OSC1和OSC2腳上;也可由外部時鐘信號來驅動。此時3.3 V的外部時鐘接在OSC1腳上,OSC2斷開或者通過一個電阻接地來降低系統噪聲。

2.3 振蕩器啟動定時器

ENC28J60內部有一個振蕩器啟動時鐘OST(Oscillator Startup Timer),上電7 500個時鐘周期(300 μs),OST期滿后內部的PHY方能正常工作。這時不能發送或者接收報文。上位機可通過檢測ENC28J60內部ESTAT寄存器中的CLKRDY位的狀態來決定是否可設置發送或接收報文。

需要注意的是,當ENC28J60上電復位或者從PowerDown模式下喚醒時,必須檢測ESTAT寄存器中的CLKRDY是否置位。只有CLKRDY置位后才能發送、接收報文,訪問相關寄存器。

評論