基于FPGA的數字視頻接口轉換器設計

由圖1可知,系統主要包括DVI接口模塊、FPGA模塊、存儲器模塊及Camera Link接口模塊。系統的功能流程為:

DVI接收器將TMDS信號轉換為單端數字信號(包括24為RGB像素信號,行場同步信號,DE信號及像素時鐘信號),并將其送給FPGA.經過FPGA相應的信號處理,將視頻數據直接輸出給Camera Link編碼器完成視頻接口的轉換。其中,FPGA的處理任務主要包括:合理控制外部大容量存儲器的讀寫,實現輸入視頻信號的幀緩存;實現視頻信號的幀頻改變、分辨率改變及色度空間轉換。測試時,系統使用普通PC機的DVI輸出接口作為視頻信號源,用標準的Camera Link采集顯示系統實時采集轉換后的信號,以驗證系統功能。

3 系統硬件設計

系統的硬件設計主要包括:DVI接口的擴展顯示認證數據 (EDID)設計,DVI接口接收電路、Camera Link接口發送電路及FPGA配置電路等FPGA外圍電路設計及大容量存儲器電路設計。

3.1 DVI接口EDI#D設計

DVI標準內含視頻電子標準協會(VESA)制定的EDID標準及DDC2B協議。DDC2B協議構建于I2 C總線技術,用來讀取接收設備所能支持的顯示格式等EDID數據。只有接收設備符合DDC2B協議,且接收設備存儲有正確的EDID數據時,計算機顯卡才 會向接收設備輸出TMDS視頻信號。

系統選用基于DDC2B協議的AT24C02B來存儲EDID數據,AT24C02B為256字節EEPROM,可存儲EDID 1.2版本或更高版本的EDID數據。EDID結構包括視頻分辨率、行場同步信號的時序特征、圖像顏色深度、視頻寬高比、版本號及設備制造商ID 等多種數據信息。EDTD 數據信息共占128個字節,被正確配置后,使用EEPROM 燒寫器將有效數據存儲在AT24C02B的前半部分地址空間,便完成了DVI接口的EDID設計。

3.2 FPGA外圍電路設計

FPGA外圍電路包括DVI接口接收電路,FPGA 配置電路,Camera Link接口發送電路。DVI接收芯片選用TI公司的TFP401A,Camera Link發送芯片選用國家半導體公司的DS90CR285,均為專用視頻編解碼芯片,接口電路遵循其參考設計進行開發即可,不再贅述。

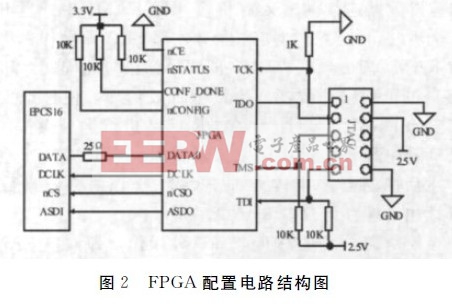

FPGA為基于SRAM 架構的可編程邏輯器件,其內部功能邏輯在系統掉電時會丟失,因此,其外圍配置電路是FPGA正常工作的保證。系統使用外部串行配置芯片(EPCS16)存 儲FPGA配置數據,以實現系統上電時的FPGA程序自動加載。FPGA 配置模式設計為主動串行(Active Serial)加JTAG方式,配置電路如圖2所示。由圖可知,該電路設計簡單,通過JTAG接口將sof文件加載到FPGA中,可實現程序的在線調試。 程序調試成功后,通過同一個JTAG接口,可將最終的jic編程文件固化到EPCS16中。

3.3 存儲器電路設計系統存儲器電路由3片SRAM 芯片組成,可實現輸入視頻信號的幀緩存功能。系統輸入的視頻信號為XGA (1024×768@60Hz)格式,一幀圖像的有效像素個數為1024×768個,而每個數字像素信號為24bits,故一幀視頻信號的有效數據總量為 1024×768×24=18Mb.目前市場上,尚無任何一款SRAM、雙口RAM 或FIFO芯片能單片滿足存儲XGA信號一幀圖像數據的要求。系統使用三片1M×16bits的SRAM芯片組成存儲器模塊組,最多可緩存兩幀XGA視頻 圖像。具體電路設計方法為:三片SRAM 的數據總線并行擴展為48位,地址總線和片選等控制信號全部相同,組成1M×48bits的大容量存儲器,可滿足系統要求。

fpga相關文章:fpga是什么

評論