基于FPGA的DVI/HDMI接口實現方案

在消費市場上,平板顯示技術的增長有助于統一接口選擇和降低成本。盡管首個高清晰度顯示器使用了模擬分量視頻接口(YCrCb),數字技術,諸如數字視頻接口(DVI)和高清晰度多媒體接口(HDMI)已經取代了大多數模擬接口。庭影院市場爆炸式的增長需要更新DVI標準。然而,需要一個龐大連接器的DVI接口限制了對數字版權管理(DRM)的支持,且缺少對單聲道或多聲道音頻的支持。為滿足演變的HDMI標準要求,它使用相同的如DVI這樣的基本信號傳輸,支持較小的連接器,以及更大帶寬(1080p分辨率)、DRM和8個通道的多格式音頻。

基于在平板領域中占主導地位的DVI和HDMI協議,原始設備制造商正在越來越多地追求他們自己的集成一種或兩種技術的產品開發。

DVI 和 HDMI標準

HDMI規范可以傳輸和接收未壓縮的數字流的音頻/視頻標準。它可以將視頻和多聲道音頻組合至單一的數字連接,節省了多條線路連接及相關成本。對于沒有音頻要求的1080i分辨率顯示,HDMI信號傳輸與DVI是向下兼容的。

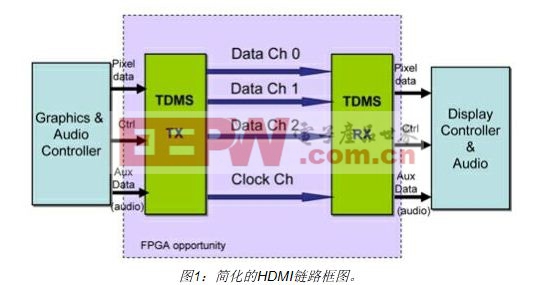

DVI和HDMI是基于稱為最小化傳輸差分信號(TMDS)的信號傳輸技術 . TMDS也有類似CML的物理信號傳輸電平(電流模式邏輯)。圖1給出了簡化的HDMI鏈路框圖。

HDMI接口是一種帶有三個TMDS通道的屏蔽電纜。默認配置是RGB ,每個通道傳送一種顏色。與DVI不同, HDMI支持亮度及色度的分量(YCbCr 4:4:4和4:2:2),并通過3個T M D S鏈路,支持多達8個音頻通道。分開的對線以1/10X TMDS比特率傳送一個同步時鐘,另外的線提供了一個低速的顯示特性,支持從顯示器到源端的通信(EDID)。另外,HDMI還集成了輔助控制功能,如熱插拔檢測和針對EDID接口的電源和地。HDMI共有29個連接。接收器恢復信號的功能限制了電纜的長度。

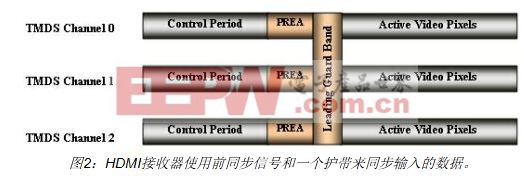

HDMI鏈路有三種工作周期:視頻數據周期、數據隔離周期和控制周期。它在視頻數據周期傳送有效的視頻,在數據隔離周期傳輸音頻和輔助數據,傳輸時使用了一系列的數據包。在任何視頻或數據周期之間,需要有控制周期。每個視頻數據周期開始時,有一個緊隨護帶的前同步信號,針對從控制周期到視頻周期的過渡,提供了非常穩定的指示。前同步是8個連續的預定義字符(10'b1101010100 , 10'b0010101011 , 10'b0101010100 ,和10'b1010101011),護帶是針對每個通道的2個連續的獨特字符(通道1 : 10b1011001100 ;通道2 : 10b0100110011 ;通道3 : 10b1011001100)。

使用DVI/HDMI實現系統

DVI和HDMI的發送和接收接口通常用ASSP來實現。本文提出了一種采用FPGA的替代解決方案。采用FPGA實現DVI/HDMI接口具有以下優點:

(1)FPGA技術使得設計人員可以將ASSP串行/解串器(SERDES)與后端定制的特殊設計功能集成在一起,以節省電路板面積。

(2)通過盡可能少地使用元器件、降低成本和功耗來增加設計的可靠性。

(3)讓設計者利用最新的技術,受益于先進的工藝技術。該標準在1999年批準后不久,開發了大量的離散DVI接口器件。由于這種制造技術是成熟的(主要是0.18微米),因此更加昂貴。

(4) FPGA擁有寬的溫度選擇范圍,具有針對工業和汽車的產品,而大多數離散的DVI和HDMI接口器件是專為消費市場而設計,往往只能在商業溫度范圍內工作。因此,對于在工業和汽車應用方面的嵌入式設計,這可能會是一個問題。

(5)FPGA設計是可移植的,使人們關注的產品使用壽命得到最大限度延長。大多數DVI器件是針對基于PC的應用,通常這些接口適合進一步集成至其他的ASSP.這種情況發生時,這些分立器件或許不再可用,因為制造商可能只愿意為個人電腦市場提供服務。

所有這些因素使得FPGA解決方案更具有吸引力,而且這也是最前沿的技術。FPGA已被證明是一種有效的解決方案,它能夠集成多種功能、縮短產品的上市時間并降低總的成本。此外,FPGA通常有很寬的溫度范圍,并有很長的產品生命周期。

針對ECP2M和ECP3器件系列,萊迪思(Lattice)半導體公司最近推出了DVI/HDMI接口的參考設計。萊迪思半導體公司的ECP2M和ECP3系列是集成了SERDES的低功耗、低成本FPGA,擁有很寬的溫度范圍。這些器件具有高達16個通道的SERDES,可處理250Mbps~3.125Gbs的數據速率,且無過采樣情況。DVI/HDMI是ECP2M和ECP3系列支持的模式之一,能夠實現這個設計是因為萊迪思已對T M D S信號傳輸構建了一個獨特的接口。在DVI/HDMI電纜中, T M D S信號是有一個外部時鐘的源同步信號。萊迪思已開發出一種技術,利用ECP2M或ECP3中內置的SERDES恢復并產生針對T M D S的合適的數據和格式。這種實現是可能的,因為內置的SERDES有250Mb/s到3.2Gbp/s的寬動態范圍。

萊迪思的DVI/HDMI參考設計集成了發送和接收功能,使得用單芯片解決方案能夠實現一些有趣的應用程序。例如,可以針對設計使用傳輸方向,從原來的7:1 LVDS顯示驅動器轉換至DVI.在接收端,用接收到的HDMI數據實現一個HDMI擴展器,然后將它格式化并通過另一種接口(如光纖或CAT5)送出。另一種應用是HD-SDI到DVI的轉換,或反之亦然。針對圖形疊加、畫中畫和分屏應用,HDCP協議的許可證可以進一步處理和管理音頻和視頻數據流。

基于ECP2M的接收功能實現

DVI/HDMI參考設計有發送和接收功能。在接收端,ECP2M利用內置模塊SERDES恢復T M D S信號,通過SERDES內的時鐘和數據恢復(CDR)電路完成這個處理。CDR電路將每個串行的T M D S通道轉換至10位,并將具有同步時鐘的數據傳送至FPGA接口,然后在FPGA中進行數據處理達到同步。這要求有三個級別的同步,分別是在本文中稱為“字節對齊”的10位同步、通道調整、多通道對齊。文章的后面討論這些步驟。接下來是自動檢測正在運行的數據流的分辨率(480p、720p、1080p或1080i),并調整物理編碼子層(PCS)參數。當在這些分辨率之間動態切換時,應保證優化運行。針對發送端,沒有必要進行字節和通道對齊。10位模式的PCS是用來使數據串行化,并與液晶顯示屏通信。

評論