基于FPGA 和USB2.0 的高精度數據采集系統設計

0 引言

隨著數字通信技術的逐步發展,高速數據采集系統已經逐步取代傳統的數據采集系統,其廣泛應用在眾多場合。新一代可編程邏輯器件FPGA 都擁有較多的IO 端口以及強大的數據處理能力,這也為高速高精度數據采集系統的研發提供了基礎條件。

1 工作原理

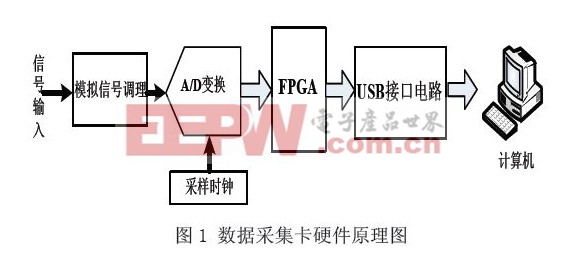

本文設計的數據采集卡硬件原理框圖1 如下所示。

如圖1 所示,前端模擬電路將外界的模擬信號轉化成為ADC能夠接收到的數據格式;高速時鐘電路提供500MHz 的高速時鐘,ADC 在此時鐘作用下,進行ADC 變換。在整個數據采集卡中,FPGA 是進行采集控制,以及數據接收的核心。FPGA 按照1 :4 的比率對將接收到的500MHz 的LVDS 差分數據流進行分流和降速。

數據分流之后由于數據速率與USB 接口數據傳輸速度不同,所以還要進行FIFO 緩沖。FIFO 的寫時鐘與串行收發器保持同步,當FIFO 緩沖器被寫滿之后,由FPGA 讀取FIFO 緩沖器中的數據,并且將數據通過USB 接口芯片傳輸到上位機中進行顯示或者存儲。

2 系統設計

數據采集卡主要包括高速A/D 轉換模塊、FPGA 主控模塊和USB 接口電路三個模塊。

2.1 高速A/D 轉換模塊

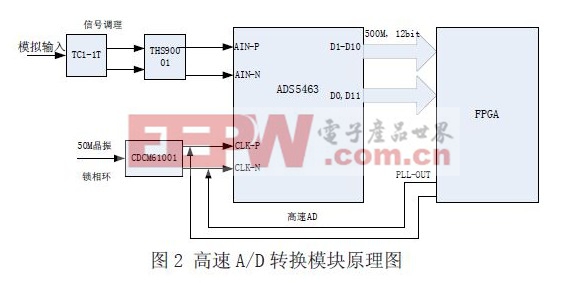

ADC 芯片作為模數轉換的核心,設計采用TI 公司推出的ADS5463,其采用流水線型結構,最高采樣速度500MSPS,精度12位,擁有高速差分數字接口LVDS.

對于高速ADC 采樣電路,模擬信號輸入接口的設計不僅要保證足夠的傳輸帶寬而且要完成將單端的輸入信號變成差分信號的功能。本設計使用射頻變壓器將單端輸入轉換為差分輸入,并通過TI 公司生產的可級聯中頻放大器THS9001 芯片實現中頻信號放大的功能。

在A/D 轉換模塊中,采樣始終的質量非常重要。在本文的設計中,采用了鎖相環芯片CDCM61001 生成采樣時鐘,并利用FPGA內部PLL 資源倍頻生成采樣時鐘作為備用的采樣時鐘。本設計是用25M 的時鐘倍頻20 倍生成500M 以LVPECL 格式的差分電平形式。

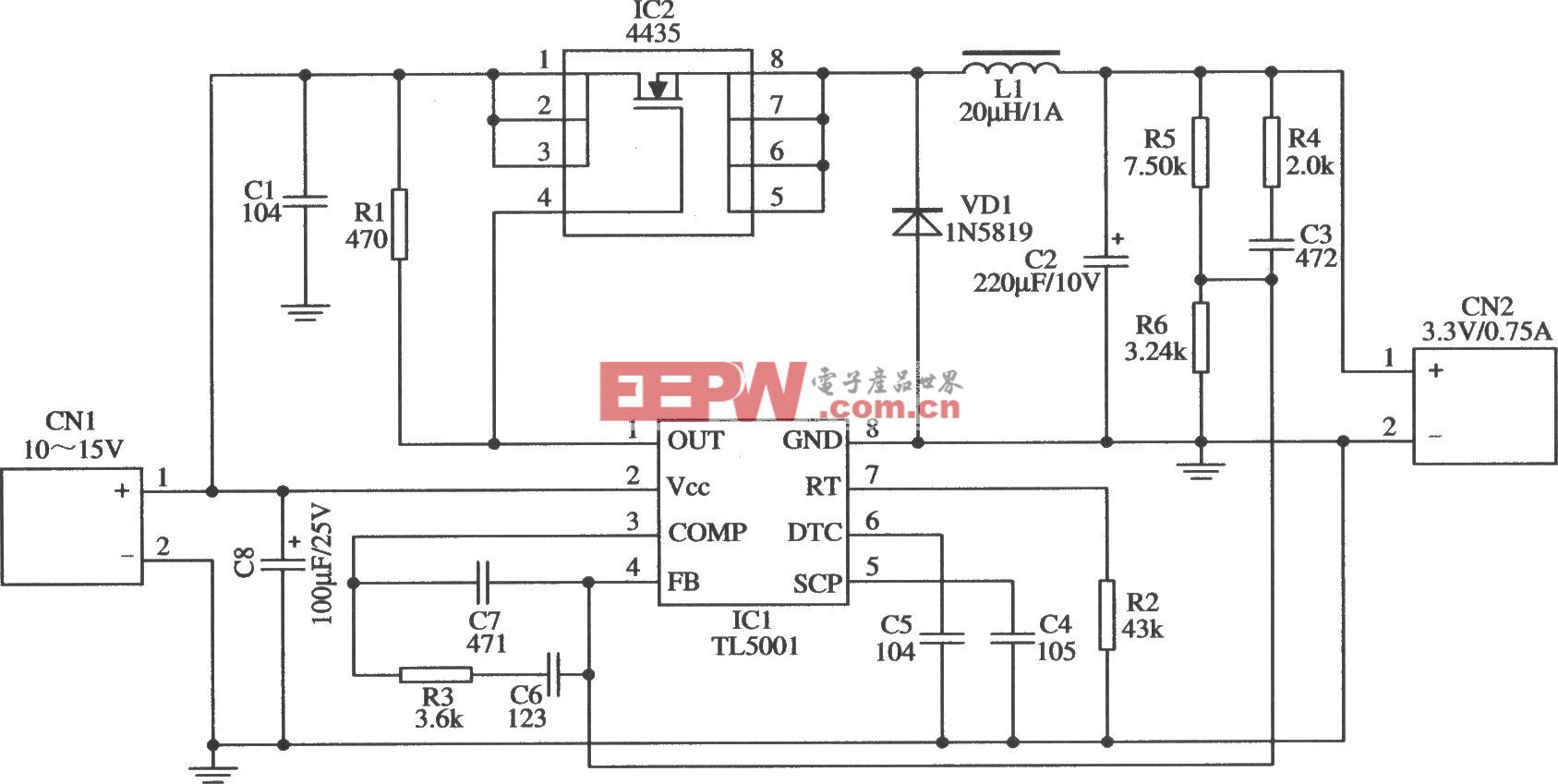

高速A/D 轉換模塊的原理圖如圖2 所示:

2.2 FPGA 主控模塊

FPGA 是整個采集模塊的控制核心,其主要的功能是接收數據,并且對數據進行降速、分流以及緩沖,并且將數據傳通過USB接口傳輸給上位機。在本文的設計設計中,選擇Cyclone II 系列的EP2C35F672C6,它屬于一款中等密度的FPGA,相比較于ASIC低得多的成本在單片機上實現復雜的數字系統。

設計使用FPGA 的Bank3 和Bank4 接收來自ADS5463 輸出的高速LVDS 數據,包括DRY(數據輸出準備好)以及OVR(數據溢出位)。Bank5 和Bank6 用于USB 接口芯片的控制,其余BANK 留作擴展之用。

在FPGA 主控模塊中,AD 輸出信號和時鐘信號被傳輸到FPGA 中的DIFFIO_RX p/n 通道上。其中p 表示正差分通道信號,而n 表示負差分通道信號。在這部分的軟件設計中,使用altvds模塊接收ADC 的輸出數字信號、始終信號,并且利用DMUX 對數據流進行串行- 并行轉換,以方便對輸入信號的后續操作。

數據流在DMUX 模塊的仿真結果如圖3 所示。

如圖3 所示,Data_in 是一路500MHz 的數據流,而dout1,2,3,4 為Data_in 通過DMUX 進行降速和分流之后的結果。從圖中可以看出,500MHz 的高速數據流經過DMUX 降速、分流之后的輸出較干凈、平滑,在高速狀態下,達到這種結果是比較理想的,對系統設計上也是很有利的。

評論