基于USB3.0電路可靠性的PTC/ESD方案

USB 3.0擁有更高的資料速率,就特別須要注意元件的電流容量以保護電路,且系統設計人員在選擇ESD保護元件時也須留意許多重要參數,包括動態電阻、箝位元電壓、擊穿電壓、寄生電容、最大ESD能力、多脈沖能力、封裝形狀、關斷狀態的阻抗或泄漏電流、設備電路配置和布局的靈活性等。

現階段,市場上有幾種不同的防靜電抑制技術,例如多層陶瓷壓敏電阻(MLV),聚合物ESD抑制器和半導體的ESD抑制技術,是否選擇正確的元件將決定USB 3.0埠的設計可靠度。由于ESD保護元件的電容、箝位元電壓和動態電阻最為重要,一些保護元件制造商已實現以最小寄生電容提高訊號完整性的產品,同時有些產品的箝位元性能也達到最大化,但代價是電容很高。

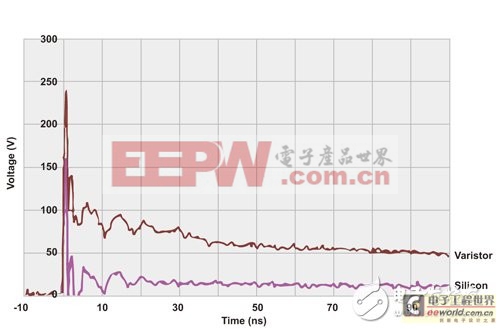

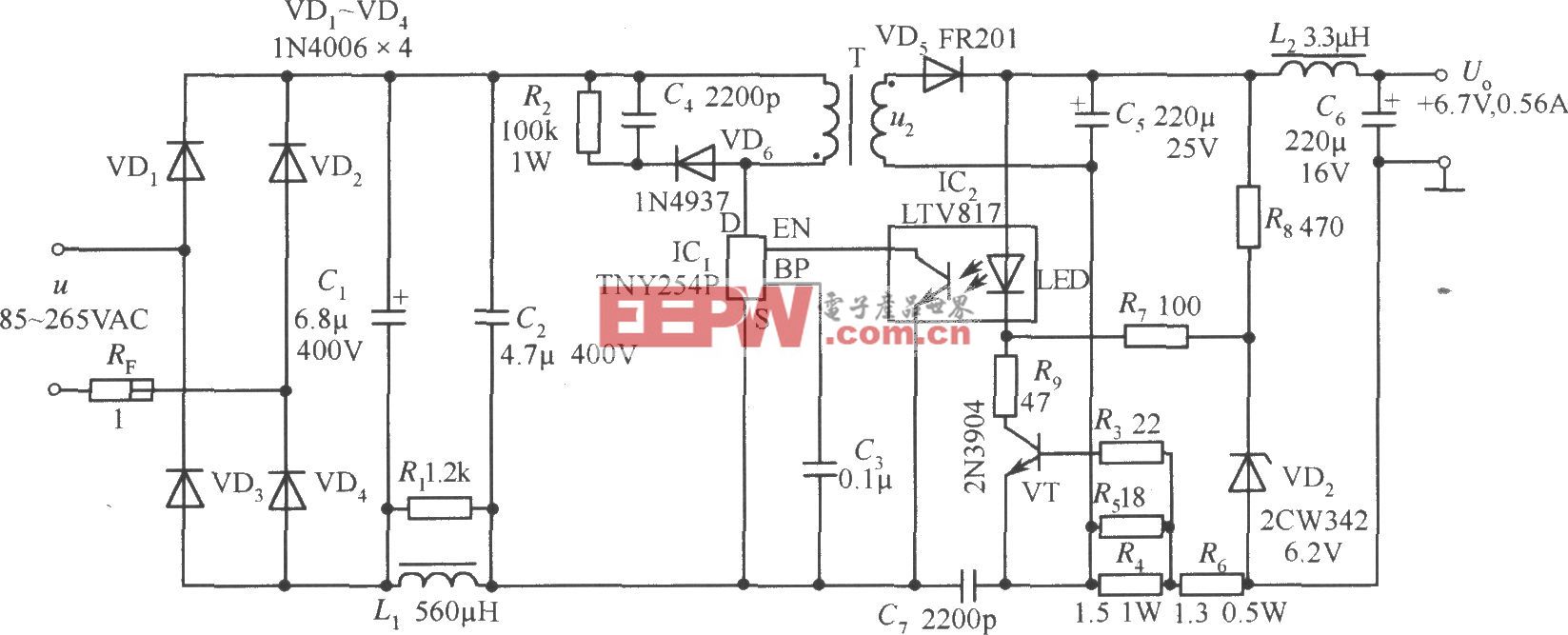

舉例來說,瞬態電壓抑制(TVS)二極體和二極體陣列有較低的動態電阻,提供卓越的箝位元性能,并能保持非常低寄生封裝電容。圖4顯示矽方案的箝位元性能與MLV ESD保護技術的比較,以矽為基礎的解決方案的箝位元電壓更低。

圖4 矽電阻與壓敏電阻的箝位元性能比較

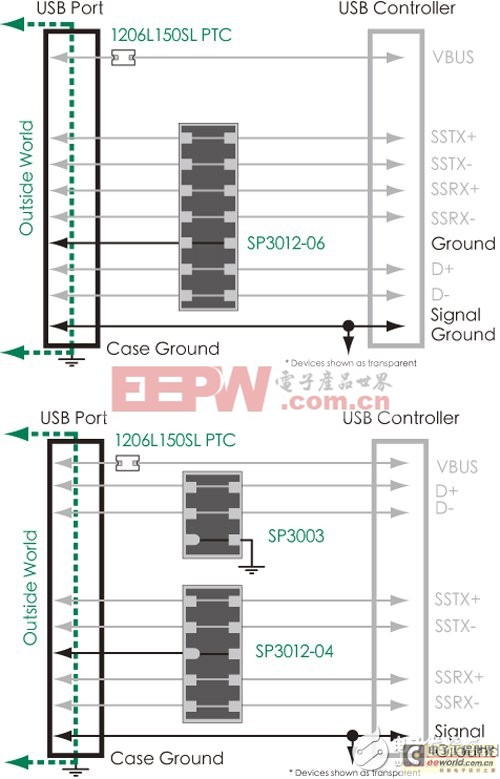

TVS二極體陣列提供多通道ESD保護解決方案(圖5),成為目前USB 3.0保護的最佳選擇。該類元件能吸收瞬態電流,并瀉放電流,同時透過雪崩或齊納二極體箝制電壓位準。如圖6所示為USB 3.0靜電保護方案架構圖。

圖5 保護USB 3.0電路的TVS二極體陣列示意圖

圖6 上為USB 3.0靜電保護方案架構圖

USB 3.0電路保護元件對維護資料完整性也非常重要,任何附加電容都可導致訊號失真,并降低訊號的可靠性。測試靜電抑制器的寄生電容對訊號完整性影響的主要方法是進行眼圖測試,此測試須重復采樣數位訊號,并在示波器上顯示出眼圖,用來定義可接受的訊號品質和依從性。

電機保護器相關文章:電機保護器原理

評論