全面解析Nios Ⅱ嵌入式軟核多處理器系統

通過對硬件互斥核,程序存儲器分區,重疊地址空間,啟動地址和異常地址的分析,提出了多處理器系統共享片上存儲器、FLASH存儲器和外設資源的解決方法,為Nios Ⅱ嵌入式多處理器系統的設計提供了有效的方法和途徑。

本文引用地址:http://www.j9360.com/article/236502.htm0 引言

基于SoPC 技術開發的嵌入式Nios Ⅱ軟核多處理器系統具有可自主設計,重構性好,軟硬件裁剪容易,系統擴充升級方便,能兼顧性能、體積、功耗、成本、可靠性等方面的要求。研發嵌入式Nios Ⅱ軟核多處理器系統,是提高嵌入式系統性價比和實用性一種有效途徑。

1 片上Nios Ⅱ嵌入式軟核多處理器系統

嵌入式系統的核心是RISC 處理器,具有代表性的RISC軟核處理器是Nios Ⅱ處理器。軟核處理器是指用編程的方法生成的處理器。是一種將硬件邏輯、智能算法、硬件描述語言和編程有機的結合出來,設計處理器硬件電路的新技術。

片上Nios Ⅱ嵌入式多處理器系統優勢在于設計者可根據的實際的需要,自主選擇Nios Ⅱ處理器的類型和數目并進行設置,對存儲器和外圍設備進行優化配置,最大限度提高片內資源和系統資源的利用率。

1.1 Nios Ⅱ處理器

由Nios Ⅱ軟核處理器構建的系統,對系統軟硬件容易進行裁剪,并可集成在一個FPGA 芯片上,構建系統和實時評估非常迅速、方便,可大大地縮短設計周期,降低設計風險。

1.2 多處理器系統類型

按共享資源分為非共享資源多處理器系統和共享資源多處理器系統兩種。非共享資源多個處理器系統中的多個Nios Ⅱ處理器完全是獨立的,不共享系統資源,處理器相互之間無干擾,系統結構不太復雜。共享資源多處理器系統在共享資源的情況下,要確保多個Nios Ⅱ處理器安全、可靠的工作,它對提高每個處理器的性能、減小體積,降低成本和功耗有利,但系統軟件的設計較為復雜。

按處理器拓撲結構分為2 種,一種是非層次結構,處理器與系統組件的連接容易;另一種是層次結構,它可根據實際需要來確定Nios Ⅱ處理器的數目,優化系統的內部結構,有效利用FPGA芯片的資源。但存在平衡多處理器的負載和任務協調的問題。

2 共享資源多處理器系統

由多個Nios Ⅱ軟核處理器,一套片上外設接口,片上存儲器,片外存儲器接口等并集成在一個FPGA芯片上,構成片上嵌入式Nios Ⅱ軟核多處理器系統的基本架構。

2.1 共享系統資源

Nios Ⅱ多處理器系統可共享存儲器、外圍設備系統資源。為了確保每個處理器共享資源,防止由于處理器之間的干擾,引起程序或數據的錯誤,導致整個系統的崩潰。Nios Ⅱ多處理器系統中使用硬件互斥核組件對共享資源進行保護處理,以協調各個處理器的正常工作,確保處理器之間不受干擾,從而提高多處理器系統的性能。

2.2 硬件互斥核

用硬件互斥核來協調各個處理器對共享資源的訪問。硬件互斥核是沒有內部功能的,是一個簡單的QSYS組件。它提供了一個協議來保證對共享資源的所有權的互斥,互斥協議是在任何時刻只有一個處理器允許訪問共享硬件資源,這樣才能有效保護多個處理器訪問使用硬件資源,防止數據的損壞或系統的崩潰。互斥核mutex提供一個原子的測試和設置操作,它允許處理器測試,如果互斥是可用的話,獲得互斥鎖處理器進行單一的操作。當處理器完成使用共享外設與互斥鎖,會釋放互斥鎖。此后,另一個處理器可以獲取該互斥鎖和共享外設的使用權。

需要注意,互斥核并沒有外設系統被多個處理器同時訪問的物理保護,運行在處理器上的軟件負責遵守互斥協議,軟件通過寫獲取互斥鎖后,處理器訪問其相關聯的共享外圍設備。多個處理器訪問一個mutex核,則每個處理器有一個唯一的標識符ID(cpuid)。Altera提供了Nios Ⅱ處理器訪問硬件的子程序,這些函數是針對mutex 核的,直接對底層硬件進行操作,每個處理器通過寫它的cpuid 控制寄存器的值到mutex 寄存器的owner 域對mutex 加鎖,而mutex 不能對HAL API 或ANSI C標準庫進行訪問。

3 片上嵌入式Nios Ⅱ軟核六處理器系統實例

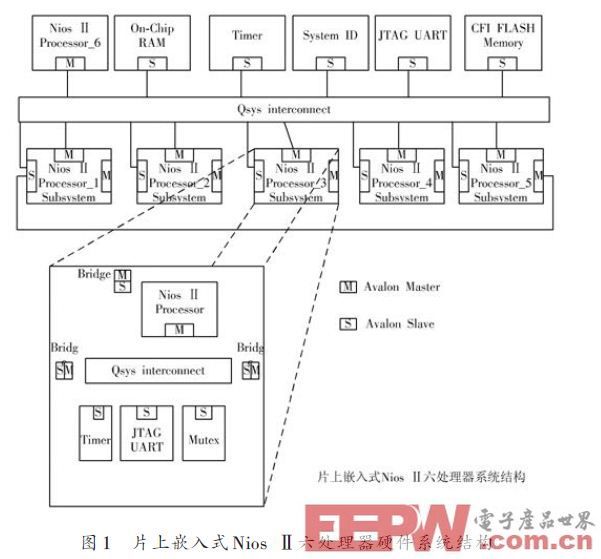

片上嵌入式Nios Ⅱ六處理器硬件系統結構示意圖如圖1所示。

3.1 硬件系統結構

由六個Nios Ⅱ處理器、硬件互斥核、片上存儲器、JTAG UART、定時器、FLASH 控制器、FLASH 存儲器、System ID、Avalon Switch Fabric總線組成系統硬件的基本結構。該系統采用層次結構,其中第六個Nios Ⅱ處理器、片上存儲器、JTAG UART、System ID、定時器、FLASH 控制和存儲器處在結構的頂層。處在底層的5 個子系統共享存儲器資源,每個子系統包含一個NiosⅡ處理器、JTAG UART、定時器和硬件互斥核,用Ava-lon-MM、Pipeline Bridges將邏輯相鄰的子系統處理器和互斥核之間連接成一個環,連接子系統與系統頂層組件之間的通信通道。

3.2 Nios Ⅱ處理器選擇和參數設置

Nios Ⅱ處理器有快速型、標準型和經濟型三種類型[3],快速型配置性能最高,經濟型配置占用片內資源最少,標準型配置的性能和占用片上資源介于快速型和經濟型之間。根據實際應用需要對系統性價比及功耗的要求,合理選擇和配置Nios Ⅱ處理器。

多處理器系統中對每一個處理器都要進行正確的設置,否則即使創建的硬件系統已通過編譯并生成,也會造成多處理器系統不能正常運行的問題。如果多個處理器使用片上存儲器為共享程序存儲器,則必須正確設計異常地址。如果使用CFI FLASH存儲器區域作為多個處理器的引導區,則必須要正確設計復位地址。使用不同類型的存儲器要正確的進行設置。

3.3 共享程序存儲器

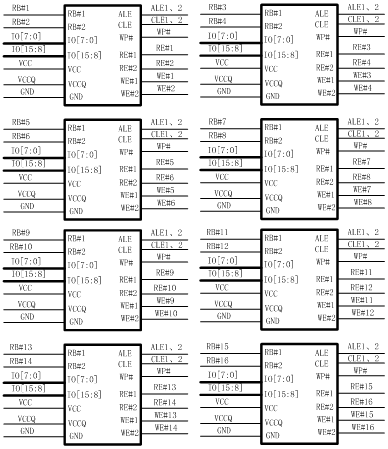

為了降低成本、功耗,簡化多處理器系統結構,實例中利用FPGA的芯片資源共享程序存儲器,六個Nios Ⅱ處理器的運行軟件共同使用片上存儲器,每個處理器的軟件位于片上存儲器所屬特有的存儲器區域。如果六個處理器的軟件在片上存儲器運行,假設每個處理器的軟件需要有8 KB的內存空間用于程序代碼和數據。這樣第一個處理器使用片上存儲器0×0~0x1FFF之間的作為其程序空間,第二個處理器使用片上存儲器0×2000~0x3FFF 之間的區域,第三個處理器使用片上存儲器0×4000~0x5FFF之間的區域;其他各個處理器所需的存儲器區域采用同樣的方法對片上存儲器進行分區。

Nios Ⅱ SBT 提供了一個簡單的存儲器分區模式,允許多個處理器的軟件運行于同一存儲器的不同區域,確保位于存儲器中的主要代碼段的鏈接和固定地址。

圖2所示六個處理器在片上儲存器的分區及代碼段的鏈接。

存儲器相關文章:存儲器原理

評論