基于FPGA的跳頻系統設計

摘要:同步技術是跳頻系統的核心。本文針對FPGA的跳頻系統,設計了一種基于獨立信道法,同步字頭法和精準時鐘相結合的快速同步方法,同時設計了基于雙圖案的改進型獨立信道法,同步算法協議,協議幀格式等。該設計使用VHDL硬件語言實現,采用Altera公司的EP3C16 E144C8作為核心芯片,并在此硬件平臺上進行了功能驗證。實際測試表明,該快速同步算法建立時間短、同步穩定可靠。

本文引用地址:http://www.j9360.com/article/235746.htm關鍵詞:跳頻;快速同步;FPGA;獨立信道法;同步頭法

跳頻通信技術具有抗干擾、抗截獲和高頻譜利用率,應用廣泛。同步是跳頻系統的關鍵技術,收發雙方只有在相同跳頻圖案相同跳變規律的同步狀態下,才可穩定建立通信。傳統同步方法主要有自同步法、獨立信道法、同步頭法、精準時鐘法。自同步法通過頻率搜索同步,難度大建立時間長;而獨立信道法通過固定信道同步,抗截獲能力弱;同步頭法的同步頭一旦受干擾,整個系統將無法工作;精準時鐘法對時鐘依賴太大,時鐘不精準將增大失步的可能。文中設計了一種基于獨立信道法,同步字頭法和精準時鐘相結合的快速同步算法,以克服上述單一同步方法使用的缺點。該同步方法能快速建立同步,且建立時間短,同步穩定可靠。

1 系統整體結構

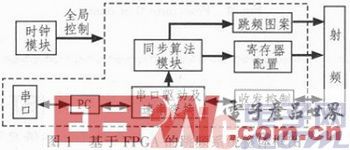

該跳頻系統基于FPGA平臺,由QuartusII軟件展開設計。系統整體設計如圖1所示。

上位機:產生數據流,時鐘模塊:控制系統各模塊時鐘,串口模塊:實現串口驅動,上位機和FPGA硬件平臺電平匹配,數率轉換,收發控制:在同步算法控制下執行幀同步檢測,根據算法協議與射頻模塊進行幀轉換。跳頻圖案:在同步算法信令控制下生成不同的跳頻序列,控制NCO頻率合成器合成相應的載波頻率。同步算法:幀同步檢測,載波同步,傳輸協議控制。同步算法通過建立同步,保持同步,同步校

驗,失步重建等,控制整個跳頻系統,實現跳頻電臺之間的同步傳輸。

2 同步算法設計

獨立信道法、同步頭法和精準時鐘法相結合構成的系統同步算法,可有效克服單一同步法的抗干擾性弱,建立時間長,不穩定等缺點。該快速同步算法的同步過程如下:

初始同步:在獨立信道法下固定分配一個專門的信道傳遞同步信息,用于雙方建立初始同步,一旦系統失去同步,則回到初始狀態重新建立同步。由于專門信道,可再次快速地建立初始同步,克服了單一自同步頭法的同步搜索復雜度高,同步建立時間長的缺點。

同步保持:初始同步建立后,發端發送同步協議幀(包括同步所需全部信息),收端根據該幀信息,進行同步校驗,控制跳頻圖案在何時進入下一跳,以保持同步。

數據通信:跳頻通信過程中,收發系統由精準的參考時鐘控制各個模塊,由協議幀控制跳頻圖案的跳變,以同步通信,有效減弱系統對全局時鐘的依賴性且同步穩定。

用上述的同步方法實現系統同步建立、保持,及數據通信的過程如圖2所示。

圖2中①②過程采用獨立信道法,在專門信道建立同步實現了初始同步建立過程;③⑤過程采用同步頭法,發送同步的協議幀,以保持同步;④⑥過程采用精準時鐘法,在相同跳變規律下的相同頻率實現數據的跳頻通信。

2.1 同步幀頭設計

系統利用同步幀頭進行同步校驗,由發端在不同狀態發送4種協議幀,收端依據協議幀信息保持和發端相同的進程進入相應狀態保持同步。該算法中設計的協議幀分別是;通信請求幀、請求確認幀、通信幀、通信確認幀,幀結構設計如圖3所示。

幀頭由國際標準定義的巴克碼構成,具備漏同步和假同步概率小的特點。前導序列和幀尾間隔保護一幀數據。其中通信請求幀和請求確認幀,用于建立初始同步,通信幀和通信確認幀在通信中,傳送協議幀進行同步校驗保證同步的穩定性。

2.2 基于雙圖案的改進型獨立信道法

傳統的獨立信道法在專門信道傳送同步信息,快速建立同步,通信失步后也跳到初始的固定信道以重建同步,降低了系統的抗干擾能力。該算法結合精準時鐘和雙圖案跳頻思想設計的改進型獨立信道法可有效克服傳統獨立信道法在失步重建信道時的低抗干擾性。

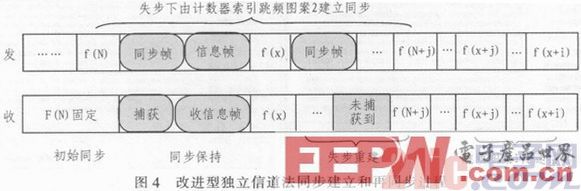

改進型獨立信道法采用雙圖案的設計思想進行初始同步的建立,該設計中的雙圖案和自同步頭法中的雙圖案有別。開機時在固定信道建立初始同步,跳頻中由跳頻圖案1傳輸每幀數據,且每次跳頻作為計數因子觸發counter_suc。通信中一旦失去同步,系統回到初始狀態,控制counter_suc產生中斷,指向短周期跳頻圖案2,由圖案2控制頻率合成器生成頻率,作為同步信道而非初始固定信道。系統中基于精準時鐘,失步時刻收發端時間信息一致,則counter_suc的中斷值一致,指向圖案2的跳頻序列也一致,則收發端頻點一致,亦可在該信道下快速建立同步。改進型的同步算法如圖4所示。

圖4中系統開機時系統在信道f(N)建立初始同步,系統失步之后,收發雙方由counter_suc指向跳頻圖案2的信道f(N+j),在該信道下再次重建同步。該系統中圖案2用于初始同步的建立,周期短搜索時間短;圖案1用于通信中傳遞信息,周期長搜索周期長。

3 快速同步算法的FPGA設計

上述快速同步算法在FPGA平臺,采用Altera公司的Quartus2作為工具,用VHDL硬件描述語言進行邏輯功能設計。

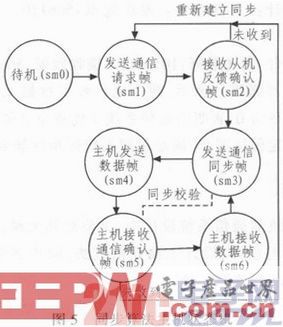

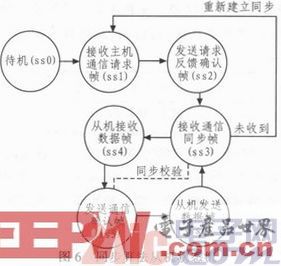

同步算法的狀態機是同步實現的核心。跳頻電臺的主機和從機狀態機如圖5和圖6所示。

圖中所示,系統上電時主機和從機處于初始狀態sm0,ss0,依照狀態機流程依次執行狀態轉移。系統的第一次握手由主機的sm1狀態發送通信請求幀實現,第二次握手則由從機的ss2狀態反饋主機通信請求確認幀實現,兩次握手在改進型獨立信道法下快速實現系統初始同步。初始同步之后,主機sm3狀態發送通信同步幀實現系統第三次握手,從機ss5狀態發送通信確認幀實現系統第四次握手,兩次握手保持通信中的同步狀態,執行圖中虛線所示的同步校驗功能。

數據通信過程由主機sm4,sm6,從機ss4,ss6狀態同步進行數據幀的收發。系統在同步保持狀態下由圖中所示環形執行狀態轉移循環進行數據通信,一旦系統中接收協議幀狀態沒接收到協議幀則系統失去同步,系統回到初始狀態重新建立同步。

4 同步性能

同步時間是指建立初始同步的時間,在該算法中主要由系統跳速Rb,跳頻間隔周期N和第一次第二次握手協議幀交換周期M決定。同步時鐘為Tsyn,則同步建立時間Ts=M×Tsyn=(M/N)xRh。本系統跳速為900跳/s時,間隔N=386個周期,協議幀周期M=665,Ts≤0.01 s,一般系統要求同步時間Ts≤0.6s,故該算法可快速建立同步。

5 跳頻系統的FPGA實現

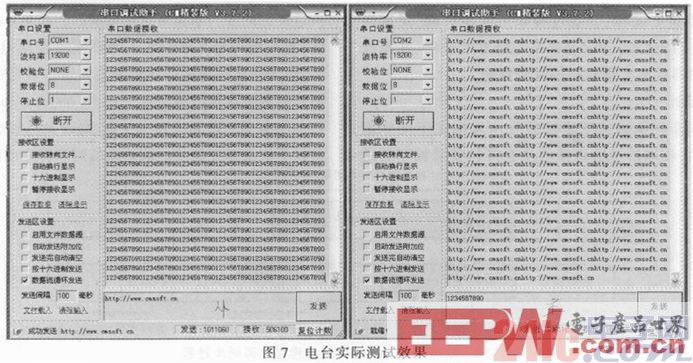

采用Altera公司的EP3C系列開發芯片作為快速同步算法的FPGA硬件實現平臺,將軟件設計實現的跳頻系統下載到開發芯片中進行性能測試。如圖7是基于該同步算法的跳頻系統測試中,兩個電臺主機和從機之間通過上位機的串口調試工具傳輸數據的統計結果,其中com1是從機通過串口連接的上位機軟件,com2是主機對應的上位機軟件。

測試統計:主機電臺:發送數據:506110,接收數據:1011060。

從機電臺:發送數據:1011060,接收數據:506110。

由串口界面統計所示,兩個電臺收發數據無誤,傳輸穩定。即誤碼率為0,表明該跳頻系統工作穩定性能良好,該同步算法可穩定保持同步,滿足跳頻系統同步性能要求。

6 結論

文中在跳頻通信系統設計中,主要對其關鍵技術同步算法展開研究與設計,設計了獨立信道法,同步字頭法和精準時鐘相結合的快速同步算法。并針對獨立信道法的抗截獲能力弱,設計了基于雙圖案跳頻的改進型獨立信道法,即短周期圖案用于同步建立,長周期圖案用于跳頻通信的實現過程,并分析了同步算法過程中的實現步驟,算法協議,設計過程等。由性能分析可知本文設計的同步算法可快速地建立同步,由FPGA硬件平臺的實際測試可知該算法可快速地建立通信,且通信過程穩定,誤碼率低,具有工程實踐意義。

fpga相關文章:fpga是什么

數字通信相關文章:數字通信原理

通信相關文章:通信原理

評論