Altera SoC FPGA架構解析

SoC FPGA器件在一個器件中同時集成了處理器和FPGA體系結構。將兩種技術合并起來具有很多優點,包括更高的集成度、更低的功耗、更小的電路板面積,以及處理器和FPGA之間帶寬更大的通信等等。這一同類最佳的器件發揮了處理器與FPGA系統融合的優勢,同時還保留了獨立處理器和FPGA方法的優點。

本文引用地址:http://www.j9360.com/article/235601.htm目前,市場上主要有三種SoC FPGA,它們的處理器都是完全專用的“硬核”處理器子系統,而不是FPGA架構中的軟核知識產權(IP)。所有這三種器件都采用了全功能ARM處理器,具有完整的存儲器層次結構,以及專用外設,啟動、運行和工作都與“普通”的ARM處理器一樣。

Microsemi SmartFusion2 SoC FPGA基于ARM Cortex-M3嵌入式處理器,主要面向微控制器應用。Altera SoC和Xilinx Zynq-7000器件使用了雙核ARM Cortex-A9應用處理器。除了處理器,SoC FPGA還有豐富的外設、片內存儲器、FPGA類型的邏輯陣列,以及大量的I/O。

這幾種可編程SoC產品表面上看來來都一樣。它們都在一個器件中集成了ARM處理器、各種外設和FPGA。而實際上,仔細的評估這些器件,更深入的了解數據資料是非常關鍵的。應針對具體應用來評估底層體系結構及其內涵。SoC FPGA體系結構非常重要。仔細的檢查和思考會發現在體系結構上有很多明顯的不同。

設計人員應如何選擇?本文介紹了在為應用選擇最佳可編程SoC時應進行的設計考慮,綜合考慮后作出工程決定。選擇標準主要集中在六個方面:系統性能、系統可靠性和靈活性、系統成本、功耗、未來發展路線圖、開發工具。

1.系統性能

SoC FPGA體系結構的兩方面最終決定在不同的單元之間能否高效的傳送數據:互聯,以及片內和片外存儲器帶寬。

SoC體系結構要考慮的第一項是Level-3 (L3)互聯。顧名思義,L3是L1和L2 Cache之下的一級數據傳輸層。L3互聯的重要性體現在,它是提高性能的交換中心。

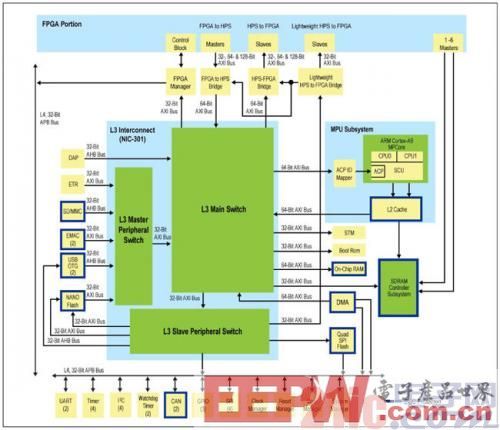

不同SoC FPGA供應商在L3系統互聯上的特性有所不同。Altera SoC FPGA提供由三種交換架構構成的L3系統互聯——L3主交換、L3主機外設交換、L3從機外設交換,使用ARM的AMBA NIC-301網絡互聯基礎結構來實現,如圖1所示。

圖1.Altera SoC FPGA互聯體系結構

Altera SoC使用精簡分層總線,無阻塞交換體系結構減小了延時。互聯設計支持來自多個主機的同時多路會話,提供足夠的帶寬,因此,每一主機能夠連續運行(“無阻塞”)。對于仲裁,能夠為每一主機分配優先級,指導總線仲裁。使用最近使用(LRU)算法對優先級相同的主機進行仲裁。其他廠家的SoC FPGA體系結構可能使用多級層次,這需要分布式仲裁,但這會帶來延時。分布式仲裁類似于有多個數據流仲裁。這種方法要求使用中心服務質量(QoS)模塊以確保主機不會擁塞。分布式仲裁也有調整問題,會與DDR存儲器控制器端口仲裁沖突。

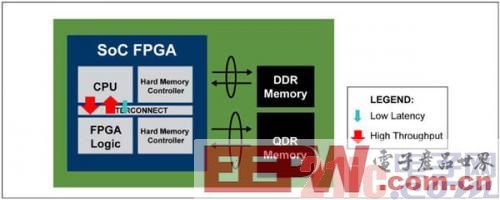

SoC FPGA體系結構最顯著的優勢是處理器與FPGA的片內緊密耦合。為實現這種性能優勢,處理器至FPGA互聯應有足夠的帶寬(寬度和速度),選擇類型合適的互聯也非常重要,這不能成為系統數據傳輸的瓶頸。

在結構方面,在其他廠家SoC FPGA器件中,數據通路和控制通路會競爭并占用帶寬。處理器需要訪問FPGA邏輯中硬件加速器并對其進行設置。如果這些控制會話過程與數據流出現競爭,那將會阻塞大吞吐量數據流,輸入數據連續處理的過程會出現中斷。相似的,寬帶數據流會延時控制信號,增加了控制延時。

為防止出現這種情況,Altera SoC FPGA采用了第二個低延時、無阻塞“輕量”互聯橋接。處理器通過這一簡單的32位ARM Advanced eXtensible Interface (AXI)接口來訪問FPGA中的控制寄存器,不會阻塞或者影響大吞吐量數據流,如圖2中的藍色部分所示。同時,處理器和FPGA之間的寬帶數據連接支持32位、64位以及128位寬度會話,如圖2中的紅色部分所示。

圖2.Altera SoC FPGA含有大吞吐量數據通路和無阻塞低延時控制通路

2.系統可靠性和靈活性

高度集成的SoC FPGA還有助于建立更可靠的系統。兩個重要的方面體現了SoC FPGA器件的不同之處:系統中有多少存儲器保護? SoC FPGA怎樣應對軟件缺陷?

對錯誤探測、糾正和監視的需求已經成為當今設計的發展趨勢。隨著存儲器容量和密度的不斷增長,對錯誤檢查和糾正的需求也在增長,也越來越重要。大部分現代系統包括專用硬件來幫助實現數據完整性。

從SoC FPGA角度看,這包括糾錯碼,即ECC保護——它不僅僅是存儲器控制器保護的一部分,而且還集成在處理器的片內存儲器、高速緩存,以及外設緩沖中。ECC電路使系統更可靠,系統不受意外數據錯誤或者數據損壞的影響。

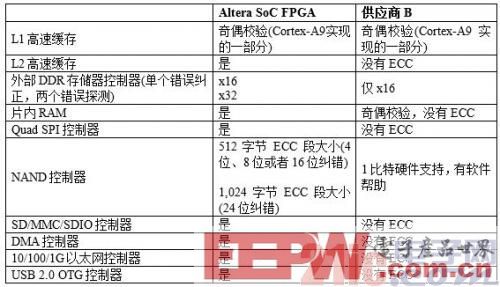

表1總結了Altera SoC的硬件ECC與其它廠家的對比

表1.SoC FPGA中的ECC

值得重點介紹的另一方面是NAND閃存。NAND閃存適用于文件系統存儲,但有時候可靠性不如NOR閃存。因此,NAND閃存的ECC被用于消除錯誤。早期版本的NAND閃存控制器包括單比特ECC保護。這雖然有一些優點,但是CPU必須參與其中,CPU必須通過軟件管理ECC,導致對性能有明顯的影響。大部分現代NAND閃存控制器都包括多比特ECC保護。特別是,在Altera SoC FPGA中實現的NAND閃存控制器包括對512字節段的4比特、8比特和16比特硬件糾錯,以及對1,024字節段的24比特硬件糾錯。這實現了功能更強更需要的保護功能,而且不會降低性能。

存儲器保護通常是先進的處理器具有的一種特性。不論是被稱為存儲器管理單元(MMU)還是存儲器保護單元(MPU),處理器的存儲器保護單元都能夠防止錯誤或者非法的處理器會話讀取或者損害其他的存儲器區域。在Cortex-A9處理器中,ARM的TrustZone技術擴展了這一保護概念,為安全敏感的系統提供了系統級方法。

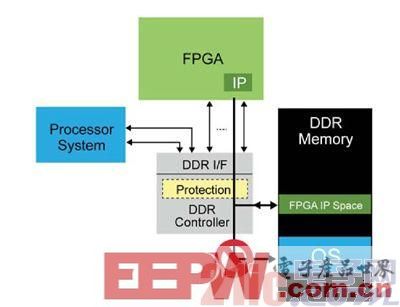

某些SoC FPGA將存儲器保護擴展到了FPGA。為什么這一存儲器保護來自FPGA,又用于FPGA呢?處理器和FPGA可以共享一個外部DDR存儲器接口,以便降低成本,減小電路板空間,節省功耗。假設定制FPGA邏輯恰好覆寫了一段屬于處理器數據、應用程序代碼,或者操作系統(OS)內核的存儲器,那么會怎樣呢?這會導致系統故障或者將處理器指向錯誤的方向。

為防止出現這種情況,為操作系統和嵌入式應用軟件指定了特定的存儲器區域,而其他存儲器區域可以專門用于基于FPGA的功能,如圖3所示。通過存儲器保護,基于FPGA的功能不會損壞操作系統或者嵌入式軟件區域。

圖3.DDR存儲器保護,處理器和FPGA共享公共的存儲器。

看門狗定時器可以防止出錯的軟件將系統阻塞。在以前的雙芯片分立方案,即處理器加FPGA的解決方案中,如果處理器運行出錯導致看門狗復位,FPGA仍然能夠運行。體系結構設計良好的SoC FPGA必須支持同樣的“獨立”行為,而且還提供選擇給系統設計人員來決定是否重新配置FPGA。在很多情況下,很關鍵的是當處理器自己復位時,FPGA邏輯需要繼續監視并響應外部激勵。因此,在這種條件下,檢查FPGA怎樣重新配置非常重要。

dc相關文章:dc是什么

fpga相關文章:fpga是什么

存儲器相關文章:存儲器原理

評論