雷達信號源的設計在雷達測試中有著非常重要的作用。DDS在相對帶寬、頻率轉換時間、相位連續性、正交輸出、高分辨力以及集成化等方面都遠遠超過了傳統頻率合成技術所能達到的水平,為系統提供了優于模擬信號源的性能。

FPGA具有集成度高、通用性好、設計靈活、編程方便等諸多優點,因此采用AD9854和FPGA來設計雷達信號源。

1 系統方案概述

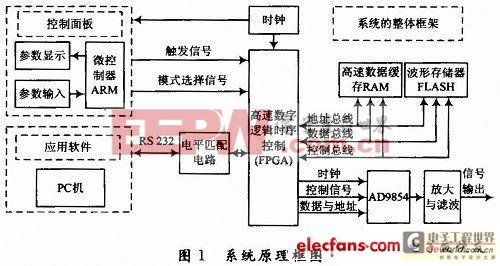

根據雷達信號源系統設計的要求,總體框圖如圖1所示。

該系統主要由FPGA時序控制部分、AD9854頻率合成部分、波形存儲三部分組成。在此重點闡述FPGA設計和AD9854硬件設計兩部分。

系統的主體部分主要由高速數字邏輯時序控制模塊(FPGA)和DDS芯片AD9854構成,還包括放大模塊、濾波模塊、存儲模塊、時鐘模塊、電源模塊。該部分通過FPGA對整個電路的數字部分進行時序控制,包括給AD9854發送數據、地址、時鐘以及控制信號。AD9854是DDS芯片,能產生所需要的信號。存儲部分采用了FLASH和SRAM;FLASH主要用來存儲波形文件,而SRAM主要是在開機時暫存數據文件。

通過控制面板發送觸發信號和模式選擇信號對系統信號產生進行控制。當FPGA接收到觸發信號時,FPGA才開始工作,并且給AD9854發送數據以產生信號。模式選擇信號是3位的二進制數,可以產生8種狀態。控制面板和FPGA通過RS 422電平相連,通過差分數據線來傳輸數據。

PC機應用軟件完成所需各種軟件的波形數據的計算,包括起始頻率FTW,頻率分辨率DFW,時間分辨率RRC等數據,然后將所得的數據轉化成.dat格式。PC通過串口與系統主板進行數據通信,通過MAX3232進行電平轉化。數據最后存儲到主板的存儲器中(FLASH和SRAM);當系統工作時,FPGA從FLASH中讀取波形文件來產生信號。

2 AD9854模塊

2.1 AD9854芯片介紹

數字頻率合成芯片AD9854是用于高端DDS技術的一款芯片,該芯片帶有兩個高速、高性能的正交D/A轉換器,可以同時輸出I/Q兩路正交信號。當參考時鐘源很精確時,AD9854能夠產生高穩定度的,頻率、相位、幅度均可編程的正弦和余弦曲線,被廣泛地應用于通信、雷達、儀器等應用領域。AD9854的高速DDS內核能夠提供48 B的相位累加器和頻率累加器(在300 MHz的系統時鐘下,可達1μHz的頻率分辨率);其中17 B的相位-幅度映射位數能夠確保該芯片優良的無雜散動態范圍(SFDR)性能。

2.2 AD9854芯片工作模式

AD9854具有5種可編程操作模式,通過改變控制寄存器(并行尋址方式下的地址為1FH)的控制位即可以選擇相應的模式。根據本方案,主要對單頻(Single Tone)模式和調頻(Chirp)模式進行探討。5種模式的選擇表如表1所示。

2.2.1 單頻模式

系統上電或硬件復位時,AD9854自動進入該默認模式,此時芯片輸出的信號是直流信號。當對頻率控制字進行設定后,即可輸出單頻信號。

2.2.2 調頻模式

此處的調頻模式即為常見的脈沖調頻模式。AD9854同時支持線性和非線性這兩種調頻模式。該雷達信號源要求既能產生線性調頻信號,也能產生非線性調頻信號,所以AD9854完全能滿足要求。脈沖調頻信號的時寬主要是由update clock來決定。當第一個update clock信號到來時,AD9854把I/O緩存中的FTW,DFW,RRC以及其他的控制字都送到可編程寄存器中,AD9854開始工作。當脈沖調頻信號結束時,通過FPGA再發送一個update clock信號,然后就把I/O緩存中的清零數據送入了可編程寄存器中。

3 系統硬件實現

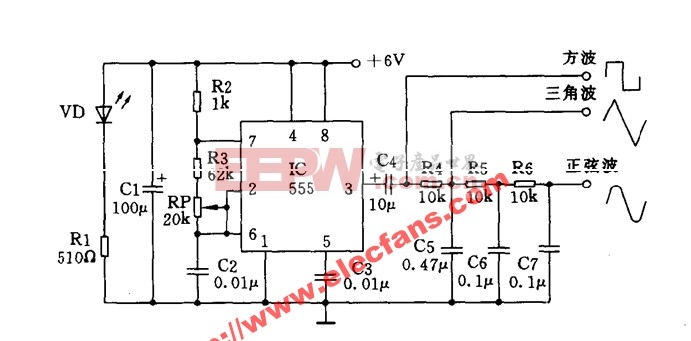

3.1 電源和時鐘設計

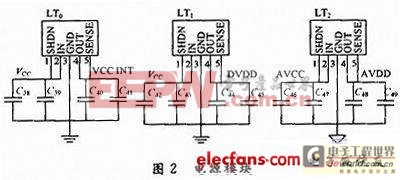

在該系統中,采用線性電源LT1764進行電平轉換,把5 V轉成3.3 V和1.5 V,為FPGA和AD9854等芯片提供電源。濾波電容分為旁路電容和去耦電容。旁路電容把前級攜帶的高頻雜波濾去,還可以有效地旁路地和電源上的地彈噪聲。旁路電容一般容值都比較小,根據諧振頻率一般是0.1μF和0.01μF。去耦電容也稱退耦電容,是把輸出信號的干擾作為濾除的對象。去耦電容一般比較大,取值為47μF和10μF。如圖2所示。

時鐘電路與FPGA的電源面要隔離開(可以在同一個層),只通過鐵氧體磁珠(ferritebead)相連。鐵氧體磁珠在低頻時阻抗很低,而在高頻時阻抗很高,可以抑制高頻干擾,這樣外面的高頻干擾不會影響時鐘芯片,而時鐘芯片內部產生的振蕩信號也不會影響到外面的電路。時鐘部分的地和整個PCB的地是一個統一的整體,不要分割。

在時鐘芯片的電源引腳處放一個容值為10μF的鉭電容,不僅可以防止由于電壓波動引起的電流涌動,還可以抑制低頻干擾;同時大電容的后面并聯一個0.1μF的小電容,且所放的位置要盡可能地靠近電源引腳,這樣可以減小外來的電源噪聲。在靠近時鐘輸出的引腳要串接一個50 Ω的電阻以減小輸出電流,提高時鐘波形的質量。時鐘線盡量少使用過孔,因為過孔使阻抗發生變化,影響信號的質量,進而產生EMI輻射和抖動問題。

3.2 存儲模塊設計

在該系統中,采用FLASH和SRAM作為存儲器。FLASH主要用于存儲波形文件,掉電時,數據也不會丟失。而SRAM是做高速數據緩存的,掉電后數據會丟失。首先FPGA從FLASH中讀取波形文件,然后再存儲到SRAM中,需要這些波形數據時候,再從SRAM中去讀取。這樣的設計是因為FLASH的讀/寫速度比較慢,而SRAM的讀/寫速度比較快。但是FLASH中的數據掉電不會丟失,而SRAM中的數據掉電要丟失。

3.3 放大及濾波電路設計

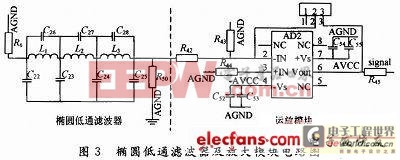

為了提高DDS信號產生系統的帶負載能力,同時實現AD9854芯片內嵌數/模轉換器輸出的電流轉換,需要在其后加入運算放大器(見圖3)。該運算放大器性能的好壞將決定信號的輸出質量及系統帶負載的能力。由于方案中信號輸出的最高頻率為120 MHz,所以應保證放大器在較高頻率范圍內具有很好的線性度,防止放大器自激。根據頻率源的設計要求,該方案中的放大器模塊應滿足以下要求:放大器的增益可調、放大器的帶寬應大于120 MHz、輸出帶載能力強、信號輸出質量較好。綜合以上要求,選擇ADI公司的寬帶運算放大器AD8014作為放大器模塊的核心器件。AD8014的主要性能特點有:低功耗;穩定增益G=1;高速,Slew Rate 4 000 V/μs,24 ns的建立時間;

在該方案中,放大電路采用串連電壓負反饋-反相比例放大電路。

采用串聯電壓負反饋將使放大器的輸入阻抗增大,輸出阻抗減小,提高電路輸出信號的帶負載的能力。在電路中,反饋電阻R16采用可調電阻,使電路的增益可調;同時在放大器的正、負電源輸入端加電容去藕濾波電路,以減小電源紋波對放大器的影響。

根據AD8014的要求,在進行PCB布線時,需在其周圍均鋪上了地網;但是,為了降低寄生電容對電路輸入的影響,其輸入腳附近沒有鋪地。在進行器件布局時,反饋電阻R16應盡量靠近AD8014的反向輸入端。

為使中頻模擬器有較好的通用性,而雷達中頻變化范圍較寬,考慮到在濾除諧波分量的同時要盡可能減少相位的不連續性,因此設計了一個帶寬為40MHz的9階無源低通濾波器。

4 FPGA實現

4.1 FPGA設計概述

FPGA用于建立與DDS芯片(AD9854),FLASH(E28F128J3A)以及SRAM(IS61LV10248)之間的聯系,主要負責以下兩個方面:

(1)發送DDS控制字并控制DDS芯片的時序;

(2)控制存儲芯片的時序,并發送或讀取所要存儲的波形數據。FPGA內部采用原理圖和Verilog HDL相結合的方式進行軟件設計。

下面重點介紹DDS控制部分的實現。

4.2 DDS控制模塊

評論