通過架構改進提高微控制器處理效率

微控制器要想處理實時I/O和外設的高數據速率和頻率,便必須擁有更高的處理效率。但這個效率不能通過提高時鐘頻率來獲得,而是要通過微控制器架構的內部改進來實現。

卸載CPU任務還有很多方法

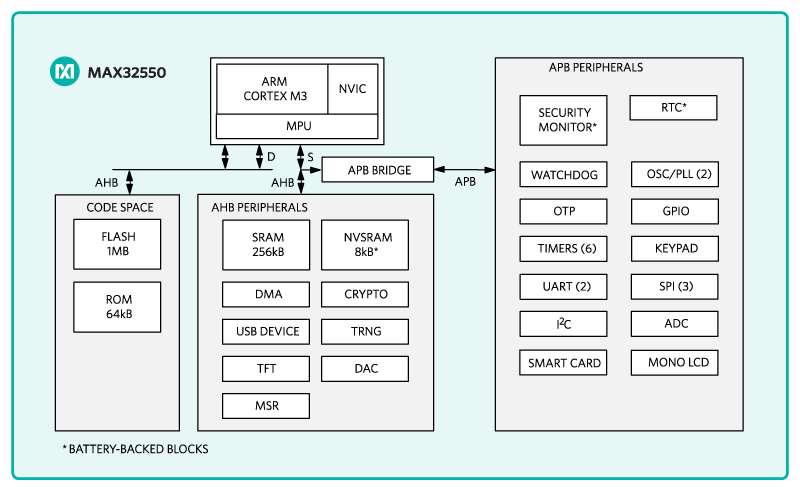

集成式協處理器在嵌入式微控制器中已獲得相當廣泛的應用,其中比較常見的協處理器是加密和TCP/IP卸載引擎。協處理器可高效卸載整個任務,或幫助執行復雜算法中的密集計算部分。例如,一個加密引擎可以把CPU上的AES計算任務從每次運算數千個周期縮減為數百個周期,而一個TCP/IP卸載引擎可以極小的CPU運行支出來終止一個以太網連。

DMA控制器通過執行數據訪問(如在后臺執行外設寄存器到內部或外部SRAM的數據訪問),從CPU卸載數據移動管理任務。DMA(Direct Memory Access,直接內存存取) 是所有現代電腦的重要特色,他允許不同速度的硬件裝置來溝通,而不需要依于 CPU 的大量 中斷 負載。否則,CPU 需要從 來源 把每一片段的資料復制到 暫存器,然后把他們再次寫回到新的地方。在這個時間中,CPU 對于其他的工作來說就無法使用。 DMA 傳輸將數據從一個地址空間復制到另外一個地址空間。當 CPU 初始化這個傳輸動作,傳輸動作本身是由 DMA 控制器 來實行和完成。典型的例子就是移動一個外部內存的區塊到芯片內部更快的內存區。像是這樣的操作并沒有讓處理器工作拖延,反而可以被重新排程去處理其他的工作。DMA 傳輸對于高效能 嵌入式系統 算法和網絡是很重要的。在實現DMA傳輸時,是由DMA控制器直接掌管總線,因此,存在著一個總線控制權轉移問題。即DMA傳輸前,CPU要把總線控制權交給DMA控制器,而在結束DMA傳輸后,DMA控制器應立即把總線控制權再交回給CPU。另外,DMA控制器還能夠承擔通信外設管理的大部分工作(見表1)。

表1 DMA控制器能夠承擔通信外設管理的大部分工作

利用DMA控制器所節省的周期數可以十分可觀:許多嵌入式開發人員都已發現自己無法以有限的微控制器資源來滿足應用的需求,直到認識了DMA,才突然明白原來還有大量額外的周期可用,數目有時甚至多達整個系統的30%到50%左右。

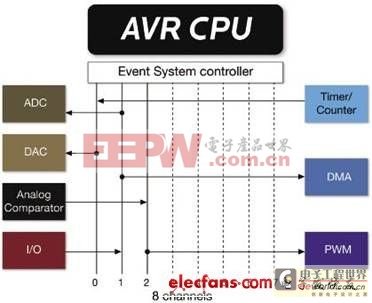

熟知事件系統(event system)的開發人員就更少了。事件系統與DMA制器協同工作,可進一步減少CPU周期的負擔,并降低總體功耗。事件系統是一條總線,能夠將從微控制器上的一個外設發出的內部信號連接到另一個外設。當有事件在外設上發生時,它就可以在一個雙周期的延時內觸發其它外設采取行動。

更確切地說,事件系統利用一個連接了CPU、數據總線和DMA控制器的專用網絡在整個微控制器上進行信號路由(見圖1)。在正常情況下,外設必須中斷CPU來激活某個行動,包括讀取外設本身。而事件系統通過直接在外設之間發送相關事件,便可有效地使CPU擺脫這些中斷所帶來的負擔。CPU是一臺計算機的運算核心和控制核心。CPU、內部存儲器和輸入/輸出設備是電子計算機三大核心部件。電腦中所有操作都由CPU負責讀取指令,對指令譯碼并執行指令的核心部件。其功能主要是解釋計算機指令以及處理計算機軟件中的數據。所謂的計算機的可編程性主要是指對CPU的編程。 CPU由運算器、控制器和寄存器及實現它們之間聯系的數據、控制及狀態的總線構成。差不多所有的CPU的運作原理可分為四個階段:提取(Fetch)、解碼(Decode)、執行(Execute)和寫回(Writeback)。

圖1 一個事件系統

靈活的卸載

DMA和事件系統配合工作,就可讓開發人員卸載整個任務,這與協處理器的作用很類似,但兩者間的關鍵區別是協處理器不是可編程的。協處理器采用硬件來執行一個已詳細定義的任務,有時甚至是可配置的;而DMA控制器配合事件系統的可編程性使其適用于從最簡單的到極復雜的各類任務。在采用DMA和事件系統的情況下,DMA負責管理整個微處理器架構上的數據傳輸;至于事件系統則控制這些低延時、高精度傳輸發生的時間。

圖2所示為事件系統與DMA共同工作的原理模塊示意圖。ADC連接一個傳感器,并會采集信號樣本。內部計數器被設置為與采樣頻率相匹配,用以提供規律且精確的時間間隔。事件系統可以直接激活ADC的采樣,而無需中斷CPU,使采樣頻率比利用微控制器的時鐘更為精確。

圖2 DMA控制器配合事件系統

事件管理可擴展為包含多個事件、連接多個外設的更復雜的配置。例如一個輸入信號(事件1)可觸發ADC采樣(事件2),并把數值存儲到DMA中(事件3),直到DMA緩沖器溢滿(事件4)。

DMA控制器和事件系統還支持多通道,使開發人員能夠配置一個與主CPU并行工作的互連結構,因此,可采用一種固定性方式來對多個并行實時任務進行協調。

評論