優化PCB布局實現高速ADC設計

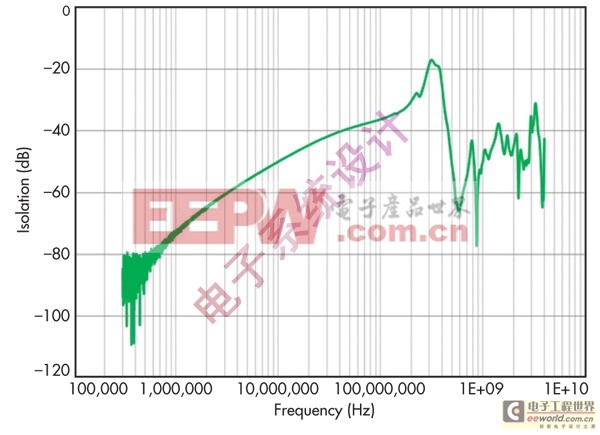

圖8:高頻處,標準FR4材料上的層間耦合可能無處不在(40~60dB),請注意隔離。對于特定設計可能足夠,但隔離應視應用而定。

舉例來說,某層上的高噪聲數字平面具有高速開關的1V信號,這意味著,另一層上將會“看到”1mV的耦合(約60dB的隔離)。對具有2Vp-p滿量程擺幅的12位模擬數字轉換器(ADC),這是2個最低有效位(LSB)的耦合。對于特定系統而言,這可能不成問題,但應注意,如果提升2位(從12位增至14位),靈敏度只會提高四倍,即8個LSB。

忽略這種平面間耦合,很可能使系統失效,或者影響設計性能。這里必須指出的是,兩個平面間存在的耦合可能超出想象。

在感興趣的頻譜內發現噪聲耦合時應注意這一點。有時布局決定了非預期信號或是平面將被交叉耦合到不同的層,在調試敏感系統時請記住這一點。該問題可能出現在下面一層。

分離地

全球模擬信號鏈設計人員最常提出的問題是,使用ADC時是否應該將地平面分離成AGND和DGND地平面?簡單回答是:視情況而定。

詳細回答則是:通常不分離。在大多數情況下,盲目分離地平面只會增加返回電流的電感,因此,它所帶來的壞處大于好處。還記得公式V=L(di/dt)嗎?隨著電感增加,電壓噪聲會提高。

隨著電感增加,您一直努力降低的PDS阻抗也會增加。隨著增加ADC采樣速率的需求繼續增長,增加開關電流的方法卻只有這些。因此,除非有理由分離地平面,否則請保持這些接地連接。

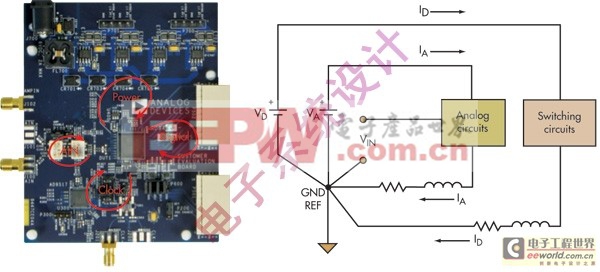

關鍵是電路合理分割,這樣就不必分離地平面(圖9)。請注意,如果布局允許將各電路保持在各自區域內,便無需分離地平面。如此分割可以提供星型接地,因此,可將返回電流局限在特定的電路部分。例如,受尺寸限制的影響而使得電路板無法實現良好布局分割的情況。這可能是為了符合傳統設計或尺寸要求而必須將惡劣的總線電源或高噪聲的數字電路放在特定區域的緣故。這種情況下,分離地平面是實現良好性能的關鍵。

圖9:對于每一應用地平面分離可能并無必要,因為魯棒的高速設計建立在固態PCB電路分區周圍而將電流局限在特定區域。

然而,為使整體設計有效,還必須在電路板的某個地方用一個電橋或是連接點將這些地連接在一起。因此,應將連接點均勻地分布在分離的地平面上。

最終,PCB上的連接點往往成為使返回電流通過,而不會導致性能降低或者強行將返回電流耦合至敏感電路的最佳位置。如果此連接點位于轉換器附近或下方,則根本無需分離接地。

本文小結

由于關于最佳布局的評論太多,所以在布局上的考慮總是令人困惑。技術和原則一直是ADI“設計文化”的一部分。在工程師傾向于借鑒以往設計經驗的同時,產品的上市壓力也使設計人員不愿去更改或是嘗試新事物。他們拘泥于風險權衡,直至系統內出現了重大問題。

在評估板、模塊和系統層面,簡單的單一接地適合于所有情況。良好的電路分割才是關鍵,這也將影響到平面和相鄰層的布局。請注意,如果敏感平面在高噪聲數字平面之上,則有可能發生交叉耦合。

組裝也是重要因素。提供給PCB車間或組裝車間的制造筆記應善加利用,從而確保IC裸露焊盤和PCB之間具有可靠連接。因組裝不良而導致的系統性能欠佳不計其數。

不過,靠近電源平面入口點和轉換器VDD引腳的去耦總是有利的。對于增加的、固有高頻去耦,應利用4密爾(mil)或間距更小的緊密電源平面和地平面。此方法不會帶來額外成本,只需花五分鐘更新PCB制造筆記。

在設計高速、高分辨率轉換器布局時,無法照顧到所有的具體特性。每一應用各不相同,有的甚至更為獨特。不過,上述關鍵點卻可以幫助設計人員加深對未來系統設計的理解。

評論