時域反射儀的硬件設計與實現----關鍵電路設計(二)

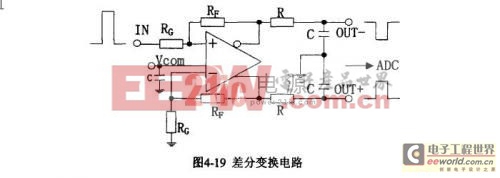

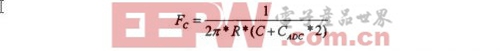

為了保證信號在模擬通道上傳輸的完整性,本設計選用了一款高性能的單端轉雙端的差分集成運放LM6550.其-3dB帶寬(bandwith)達到了400MHz,壓擺率為3000V/us,輸入噪聲小,信號失真典型值為70dB,同時具有響應快,功耗低等特點,滿足驅動高性能ADC的需求。在圖中助和RF用來控制信號放大倍數,在這里的差分電路僅僅做單端到雙端的變化,因此RG和RF都選用500Ω的電阻,即不做信號放大處理。Vcom幻以端是用來控制輸出差分信號的共模電壓,因為模數轉換器要求輸入差分信號的共模電壓在1.9v~2.IV之間,所以通過Vcom來設置差分信號的共模電壓,這樣輸出的差分信號就能與ADC的共模輸入相匹配。從運放輸出的信號在連接到ADC之前經過了一個簡單的電阻一電容(R-C)濾波器,用來消除或者減輕混迭失真的影響。如果已知濾波器的截止頻率FC,則可以通過下面式子來確定濾波電路中電阻和電容的大小。

式中CADC為ADC的輸入電容。如本設計中設濾波器的截止頻率為100MHz,電阻R取50Ω,CADC的大小為4pF,則計算出的電容大小約為25pF.

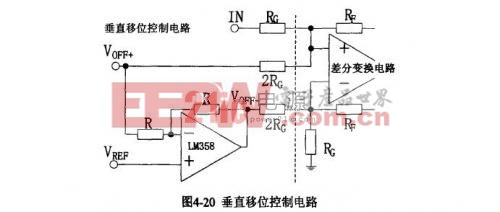

垂直位移電路用來將信號做垂直方向上的移動,對于多信號的顯示有很多大的幫助。本設計的垂直位移電路并不是將單獨將信號經過一個垂直位移電路,而是把垂直位移電路與差分變換電路相結合。即在差分運放的正向和反向輸入端引入一對以1VDC電壓為中心相互對稱的垂直移位電壓,該電壓是通過加法的形式盛加到被測信號上的。而差分運放的輸入端實際上也可以看作是雙端輸入模式,這樣當在輸入端加上一對信號時,實際的垂直移位電壓就是這兩個輸入電壓之差。

比如當正向輸入電壓為1V時,反向輸入電壓也是1V,則垂直移位電壓為OV,即信號不做垂直移位;當正向輸入電壓為1.5V時,反向輸入電壓是0.5V,則垂直移位電壓為1V,即信號向上移動1V的垂直位移,相當于屏幕上的十大格。同理當正向輸入電壓和反向輸入電壓分別為0.5V和1.5V時,信號向下移動了10大格。

在實際應用當中,信號的上下移動范圍沒有必要做到±1Odiv,因為整個顯示屏的波形顯示區域也只有±4div,因此將信號的上下移動范圍做到±5div即可滿足觀察的需要,垂直移位控制電壓就被限定在0.75V---1.25V之間變化。又因為垂直位移的控制電壓都是通過DAC來產生的,DAC的輸出范圍為0V-2V,垂直移位控制電壓的變化區間僅僅為DAC輸出變化范圍的四分之一,并沒有有效的利用DAC的輸出,可能會引入一定的誤差。為此根據運算電路中的加法規則,設計出如圖4-20所示的電路。

為了有效利用DAC的輸出,在電路設計上取垂直移位控制電路與差分變換電路之間的連接電阻兩倍與差分變換電阻中的RG,則經過運算以后,疊加到差分變換電路端的垂直位移電壓降低到原來的一半,此時如果VOFF+等于1.5V,則VOFF-等于0.5V(VREF等于1V,由DAC提供),疊加到差分變換運放的正、負輸入端后,電壓分別降為0.75V和0.25V,兩者相差為O.5V,正好對應于屏幕上向上移動了5div,滿足了設計要求,因此為了使信號在垂直方向上位移達到±5div,只要使VOFF+的變化范圍在0.5V-1.5V之間即可。VOFF+直接由DAC送出,而DAC的最小步進為2mV,最大步進通過軟件可調。如果采用最小步進的形式,VOFF+變化2mV時,通過運算以后,疊加到脈沖信號的垂直移位電壓也只有2mV,僅僅對應屏幕上方的半個像素點(每個像素點對應4mV),這樣上下移動的速度會很慢,且實際意義不大,為此將DAC的輸出控制信號的步進該為4mV,則可滿足要求,用戶在上下移動信號時,每按一次向上或向下鍵時,信號都可以向上或向下移動一個像素點。

評論