時域反射儀的硬件設計與實現----關鍵電路設計(三)

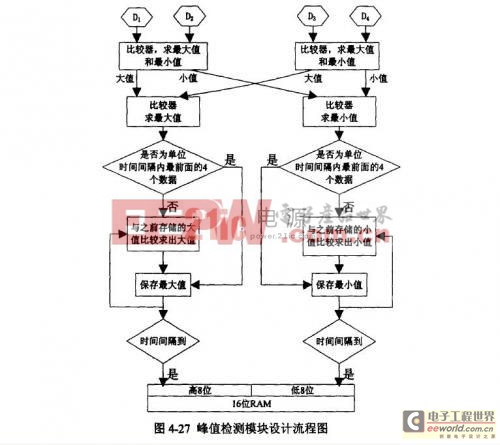

在時域反射測量中,在高速時基情況下,如100ns/div--5ns/div之間,屏幕上的一列對應了ADC單次采樣采集到的數據,即點對點形式,此時ADC也處于最高速采樣狀態下(250MSPS),當時基為20ns/div時,采樣率仍保持在250MSPS,此時屏幕上的單個像素點對應的時間間隔為5ns,對應了兩次采樣時鐘,即兩個數據確定了屏幕上的一列圖形,如果這兩個數據相同,則對應屏幕上的一點,如果不同,則對應屏幕上同一列的上下兩個或是連成一小段的像素點。當時基為500ns/div,如果采樣率仍為250MSPS,則單個像素點的時間(20ns)對應5次采樣的數據,如果采樣率為200MSPS,則單個像素點的時間(20ns)對應4次采樣的數據。又因為為了降低功耗的目的,在1us/div以后都采用了100MSPS,單個像素點的時間(20ns)對應了以4為倍數的采樣數據。為此在500ns/div時也采用200MsPs,這樣在進行峰值檢測的時候可以一次將4個數據送到高速比較模塊做流水線比較,并在規定時間周期內找到最大值和最小值。4個高速數據的峰值比較電路設計流程如圖4-27所示。

在FPGA內部,峰值檢測模塊電路由于采用了流水線的模式,因此用了較多的8位并行D觸發器、8位比較器和8位兩路選擇器來實現。雖然占用了一定的FPGA的內部邏輯單元(LB),但卻保證了大量數據的高速連續處理,且不丟失有用的數據,唯一的缺點就是實時性不強,即4個數據的比較需要經過好幾次時鐘(每個時鐘為周期為4*4ns)以后才能找到最大值和最小值,即有一定的延時性,但并不影響波形的正常顯示。因此這種流水線的操作方式實際上是一種利用空間換取時間的方式。整體設計模塊如圖4-28所示。

在峰值檢測模塊當中,輸入端有兩個控制輸入,CLK_NUM和OVER_4.OVER_4表示峰值檢測在單位時間內總共多少個數據進行比較,因為在時基為500ns/div和1us/div下,一次只進行4個數據的比較,就要輸出最大和最小值,而在Zu叮div以后都是要進行大于4個,且以4為倍數的數據的比較,而模塊單次只能比較4個數據,因此用OVER4來控制總共比較的數據是否大于4,大于4則OVER_4為1,反之為O。CLK_NUM用來控制單位時間間隔內到底有多少個數據進行比較,如果CLK-少舊M的周期為16ns,則只有4個數據比較,此時OVER_4也為0,當CLK_NUM的周期為16ns的倍數后,則會有4的倍數個數據進行比較。

實際上CLK-少舊M的周期與時基是相聯系的,如時基為500ns/div,則CLK_NUM的周期為20ns,又因為此時的采樣率為20OMSPS,所以只有4個數據比較,當時基為1us/div,CLK_NUM的周期為40ns,采樣率為100MSPS,所以同樣只有4個數據比較,而當時基為2us/div,CLK_NUM的周期為80ns,采樣率為100MSPs,就會有8個數據進行比較,而在比較的過程當中,先進去的4個數據會比較出一個大值和小值,這兩個數據被默認為最大值和最小值暫時保留下來,直到與后進來的4的數據比較出的大值和小值繼續做比較,最終確定最大值和最小值。表4-3給出了在不同時基情況下起用峰值檢測模塊控制信息相關對照表

評論