PDP控制電源的設計分析

隨著人們對大屏幕彩電的需求不斷增加,等離子顯示器(PDP)由于其體積小、視角寬、主動發光、亮度高、環境適應性好等獨特的優點,在競爭中占有相當的優勢,隨著價格的降低,它必將進入家庭,有著巨大的市場需求。等離子顯示器主要由顯示屏、屏蔽玻璃、電源、數字電路、驅動電路、外殼等部件組成,其中電源擔負著屏內所有電路和顯示屏的供電,其技術含量高,功能復雜,為滿足等離子顯示器的安全要求,需要進行精心設計和嚴格測試。

電源輸出特性

為了適應全球輸入電壓范圍,交流輸入電壓為85~276V,經過EMI濾波、整流后采用有源PFC作電壓預調整,共有8路輸出電壓:地址驅動電源Va,屏驅動電源Vs,邏輯控制電源Vcc,輔助電源(3路),風扇電源,待機電源Vsb,其主要輸出特性如下:

屏驅動電源(Vs)輸出:165~185Vdc(可控),自動設置,Vs=165+10×Vrs,Vrs為參考電壓,在0~2V之間,由PDP提供,平均電流Is為1.5A,瞬時最大電流Isp為12.0A;

地址驅動電源(Va)輸出:55~65Vdc(可控),自動設置,Va=55+5×Vra,Vra為參考電壓,在0~2V之間,由PDP提供,平均電流Ia為1.8A,瞬時最大電流Iap為3.0A;

邏輯電路電源(Vcc)輸出:5Vdc(可控),瞬時最大電流Icp為5.0A;輔助電源輸出:+5V,3.5A;+12V,1A;-5V,0.5A;12V風扇電源(Vfan):電流為0.5~1.0A;5V待機電源(Vsb):電流為0.5~1.0A。

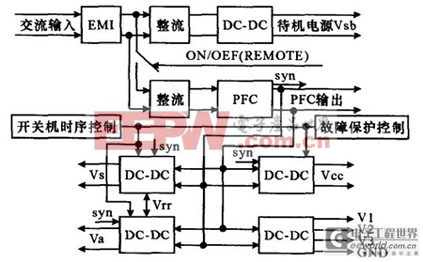

地址驅動電源Va和屏驅動電源Vs分別受PDP控制,而且有時序要求,所以采用兩個獨立DC/DC變換器;對于待機電源Vsb,在PDP不工作即其他所有輸出均關斷時仍然工作,所以Vsb采用一個獨立的DC/DC變換器;Vcc與Vs和Va是共地的,為避免地線上的干擾,輔助電源組采用單獨一組DC/DC變換器,輸出內部共地,同時為了避免差頻干擾,對大功率的Va和Vs變換器采用頻率同步的工作方式(同步于PFC電路)。各變換器的邏輯關系及工作時序如下:

a.交流上電后,待機電源Vsb開始工作;

b.遙控開機后,先吸合繼電器,PFC輸出直流電壓,輔助電源、PDP邏輯控制電源Vcc工作;

c.屏控電路初始化后,發出可啟動高壓驅動開啟電平Vrr到PDP電源,Va和Vs啟動工作;

d.遙控關機時,屏控電路先關閉Vs和Va,后關Vcc和輔助電源;

e.遙控關機后,待機電源仍然工作,以便下一次的啟動。

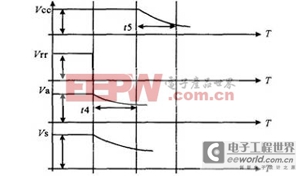

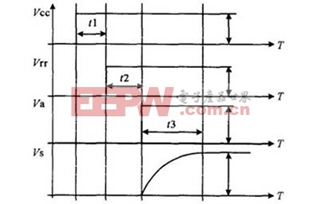

其開關機時序如圖1(a)、(b)所示。

(a) 開機時序

(b) 關機時序

圖1 開關機時序圖

圖1中的t1為PDP電源內部高低壓之間的啟動延時,大約為110ms,Vrr是高壓封鎖信號,在Vrr為高電平之后即有高壓輸出,圖中的t3表示Vs(165V)的軟啟動時間,大約為300~800ms,而Va(65V)無軟啟動。t4和t5僅代表關機時的先后順序,其本身數值的大小和負載的情況密切相關,在滿載情況下t4大約為450ms,t5大約為260ms。Vs和Va變換器是一起開機、一起關機,當前兩路中有1路保護(過流、過壓、過熱)時,則將該兩路變換器全部關斷,但不關Vcc變換器。當Vcc變換器發生故障時,將Vs和Va變換器與Vcc變換器同時關斷,整個電源的結構框圖如圖2所示。

圖2 結構框圖

電路設計

為了滿足PDP電源的上述特性要求,每種電源都需要不同的電路結構,下面詳細論述各個電路的設計。

EMI電路、有源功率因數校正電路和待機電源

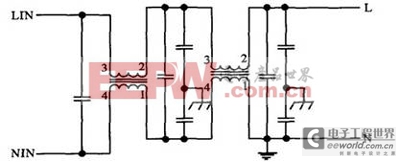

為了滿足全球化需要,PDP電源必須滿足各個組織的EMI測試要求,根據阻抗匹配采用了如圖3所示拓撲結構的EMI濾波器,經過參數優化和PCB優化,其傳導輻射通過了CLASS B標準,有源功率因數校正電路采用了UC3854作為主控芯片,功率因數達到99%,待機電源采用PI公司的專用待機電源芯片構成單端反激變換器。

圖3 交流輸入濾波電路拓撲

輔助電源

輔助電源采用UC3844組成單端反激變換器,電壓分別為一組5V/3.5A、-5V/0.5A,一路12V/0.5A,一路12V/1.0A,5V主控。

地址驅動電源Va和屏驅動電源Vs

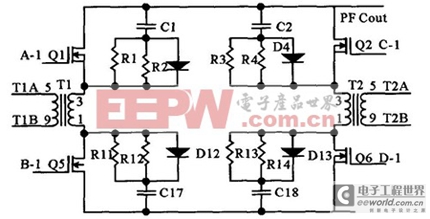

此兩路電源功率都比較大而且受控,因此采用兩路相同結構的獨立雙管雙正激變換器。我們以地址驅動電源Va為例進行設計,該路功率為120W,輸出55~65Vdc(可控),自動設置,Va=55+5×Vra,Vra為參考電壓,在0~2V之間,由PDP提供。當Vra為2V時,對應Va的輸出為65V。其控制電路采用SG3525芯片,把Vra電壓經過分壓和濾波處理后加到SG3525的1腳上對輸出電壓控制。主拓撲采用雙管雙正激變換器,特點是器件應力小,不存在剩磁問題,電路簡單,避免直通問題,圖4為雙管雙正激變換器的原理電路。

圖4 雙管雙正激變換器的原理電路 在圖4中,PFCout為功率因數校正的輸出,為400V。每路正激變換器由兩只MOSFET構成,這種雙管正激可降低開關管耐壓要求。與單正激變換器相比,雙正激變換器在使輸出功率增大的同時還帶來如下好處:①輸出濾波電感工作頻率為兩倍開關頻率,這使得其大小相對減小;②變壓器原副邊變比為單正激的兩倍,可選用低耐壓的輸出整流二極管。實際使用的開關頻率為80kHz,開關管驅動采用脈沖變壓器耦合隔離方式,這樣可減小主電路對控制電路的干擾。每只MOSFET附近的RCD電路為吸收緩沖電路,可以有效吸收開關過沖,其參數值由開關頻率和實際電路決定。當Po(單路)=65W時,其磁性元件設計如下:

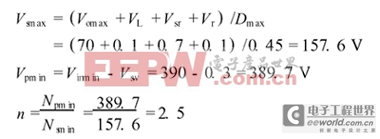

設整流管最大壓降Vsr≤0.7V,電感繞組的最大電阻壓降VL≤0.1V,其他線路最大壓降Vr≤0.1V,原邊MOFET及線路壓降Vsw≤0.3V,變壓器效率η≥98%。其他參數為:

Vs:變壓器副邊電壓

Vp:變壓器原邊電壓

輸入電壓:Vin=390~400V

輸出電流:Io=1A

輸出電壓范圍:Vo=50~70V

輸出功率:Pomax=70W

最大占空比:Dmax=0.45

開關頻率:f=80kHz

導線的電流密度:J=4A/mm2

鐵芯磁通密度變化量:ΔB=0.2T

(1)計算匝數比

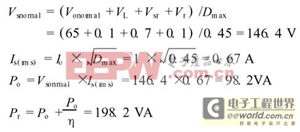

(2)計算總視在功率

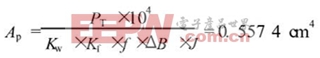

(3)計算鐵芯窗口面積乘積

Kw:變壓器窗口系數,窗口系數先粗略取0.4,本設計中原副邊繞組均采用銅線; Kf對于雙管正激電路可由以下公式算出:

![]()

(4)選擇磁芯

根據Ap查磁芯手冊,確定磁芯結構為EE42/21/15,磁芯材料為西門子N67材料,有效截面:Ae=234mm2,窗口面積:AW=250mm2,Ae×AW=5.85cm2>Ap。

(5)計算原邊、副邊繞組匝數

原邊開關管為MTP4N80,額定電流4A,耐壓800V。輸出整流二極管D1~D4采用4只快恢復二極管DSEI1206A,其中2只并聯使用作為續流二極管。DSEI1206A的反向軟恢復特征使得輸出尖峰電壓減小外,反向恢復電流折算到原邊也小,使得原邊MOS2FET開通損耗減小。在輸出電壓65V,輸出電流1A時,變壓器溫升小于30℃,效率為93%。

測試結果

PDP電源設計完成后需要進行高低溫沖擊試驗、負載特性、功率因數、EMC等測試,其滿載功率因數測試為>98%,以下為其他各個測試項。

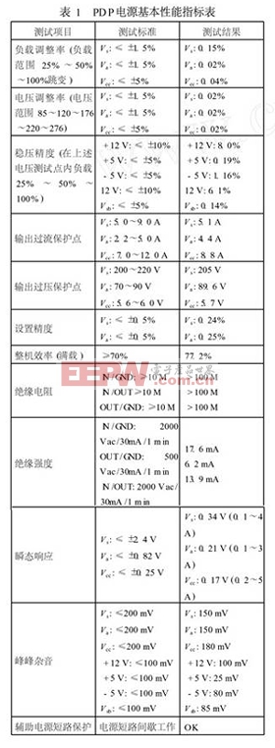

基本性能指標

PDP電源基本性能指標表如表1所示。

環境測試

A.低溫測試:-5℃時,電源能啟動且可以正常工作,測試負載調整率、電壓調整率、穩壓精度、輸出過流保護點、輸出過壓保護點、設置精度、峰峰雜音等項目。

B.高溫測試:50℃時

評論