使用一塊板的話應該產生更低的抖動結果����。

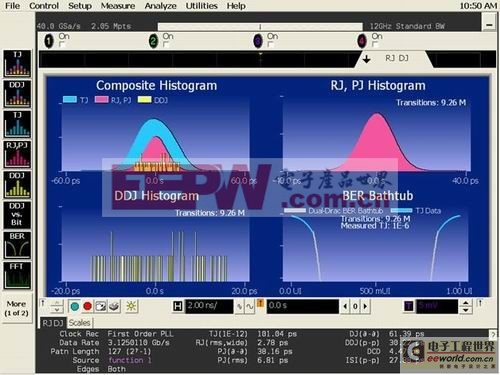

圖4:抖動測試結果。

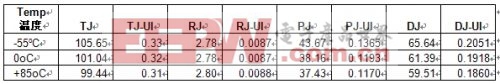

表1

ispClock 5406D的配置存儲在片上非易失性存儲器中�����,可通過JTAG接口進行再編程。器件上的許多功能還可以通過I2C接口進行“即時”修改�����?��;趇spClock 5406D的系統的可編程特性支持許多附加功能�����,包括:TH和TCO時序裕度測量,有助于設計穩定性的測試�;使用發送和接收通道間獨立的偏移時鐘的裕度測試�,提高了可制造性���;在數據有效窗口的中心進行準確的時鐘對齊�����,增強了系統的可靠性�����。

分頻器相關文章:分頻器原理

晶振相關文章:晶振原理

評論