智能手機省電秘訣:看如何從設計源頭來降低功耗

技術壁壘較高的是低電壓化。雖然半導體芯片截至90nm工藝一直在隨著微細化順利降低電壓,但之后SRAM的誤動作成為瓶頸,低電壓化越來越難以實現。目前的便攜終端用處理器的標準電壓只降到1.0~1.1V左右,最小驅動電壓降到0.8~0.9V左右。因此需要從根本上改進電路技術。

推進這類研究的是美國英特爾。該公司試制出了電力效率在閾值電壓附近最高的x86處理器“Claremont”。這是通過開發能以0.28V的極低電源電壓正常運行的電路群來實現的。以接近閾值電壓的0.45V電源電壓運行時,工作頻率為60MHz,電力效率最大為5830MIPS/W(整體耗電量為10mW)。以1.2V運行時,工作頻率最大為915MHz,電力效率為1240MIPS/W(整體耗電量為737mW)。

漏電功率對策也在推進

要想提高電力效率,還必須削減漏電功率。韓國三星電子在“Exynos”處理器上采用32nm工藝制造技術時,導入了high-k柵極絕緣膜/金屬柵極(即HKMG)。

與32nm工藝中未導入HKMG時相比,柵極漏電流降至約1/100,整體漏電流降至約1/10。另外,三星電子還首次采用了基板偏壓技術*。目的是根據裸片上的漏電功率和性能的監控信息,減小制造偏差造成的性能下降和漏電功率。

*基板偏壓技術=在硅基板上加載偏壓以動態控制閾值電壓的技術。通過加載負電壓提高閾值電壓以暫時抑制漏電流的后基板偏壓,或者通過加載正電壓降低閾值電壓以暫時提高速度的前基板偏壓。

為盡量削減正常處理時無需消耗的電力,而實施的對策是根據負荷改變工作頻率和電壓的DVFS*,以及以電路塊為單位的電源切斷和時鐘切斷操作。處理器本來就導入了以動態控制電力為目的的技術。通過將這些技術用于細微之處,使負荷和耗電量走勢基本上呈現同樣的曲線走勢。

*DVFS(dynamic voltage and frequency scaling)=在LSI中,通過根據處理負荷等動態控制電源電壓和工作頻率,從而削減耗電量的方法。以LSI根據軟件指示變更設定的形態運行。

從細微之處入手,瑞薩移動的做法可謂典型。該公司的母公司瑞薩電子在用于傳統手機的應用處理及基帶處理整合型處理器“SH-Mobile G”系列中,將DVFS應用到了CPU內核中,并對電源域和時鐘系統進行了細分化。

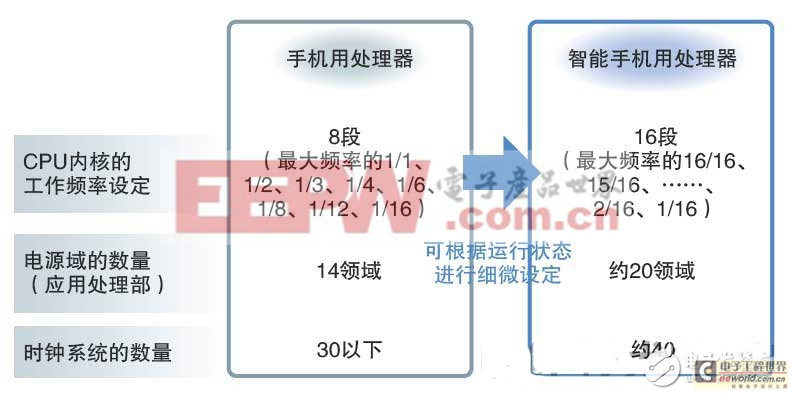

而瑞薩移動面向智能手機開發的“MP5232”則對CPU內核的工作頻率設定以及電源域和時鐘系統則進行了更加細致的劃分(圖7)。“由于必須配置電源開關,因此并不是只要細分就完事了。我們設想了智能手機的使用情況,找到了最佳劃分點”(瑞薩移動移動多媒體事業本部SoC事業部事業部長服部俊洋)。

圖7:根據利用情況對電力進行極其細微的控制

瑞薩移動面向智能手機開發的“MP5232”與用于傳統手機的處理器相比,可以根據利用情況對電力進行極其細微的控制。CPU內核的工作頻率設定、電源域的數量以及時鐘系統的數量均大幅增加。 對每個CPU內核控制頻率

美國高通的“Snapdragon”系列采用根據多個CPU內核進行DVFS的方式。向一個內核施加較大負荷時,如果其他內核的負荷較小,則會削減負載較小的內核的工作頻率(圖8)。其他半導體廠商則采用對內核群統一進行DVFS的方法,即根據處理負荷統一改變多個CPU內核的工作頻率。

圖8:按照多個CPU內核進行DVFS

高通在“Snapdragon”系列的多核產品中,按照各CPU內核進行了動態控制電壓和頻率的DVFS。通過向各CPU內核供給其他系統的電力和時鐘,提高了對處理負荷的追隨性。

按內核進行DVFS的方法存在電源電路部件增加的問題,不過“該方式能防止當單線程的處理負荷較大時,其他內核以不必要的高頻率運行狀態,我們判斷這樣做的優勢更大一些”(高通日本CDMA技術營銷及業務開發統括部長須永順子)。除了雙核產品外,四核產品也采用相同的方式。

DVFS和電源切斷的徹底實施在基帶處理LSI方面也得到了推進。尤其是“在整合型處理器中,基帶處理部也容易細微地控制電力”(高通日本的須永)。不僅是成本和安裝面積,耗電量也可能成為選擇整合型處理器的理由。

適當使用效率各異的CPU

今后,處理器將導入的新低耗電量化舉措之一是電路的“混合”化。在智能手機中,“所要求的處理動態范圍比傳統手機大幅擴大。今后還會進一步擴大”(瑞薩移動的服部)。在處理負荷非常小時和非常大時區分使用最佳電力效率的電路——這類對策將得到推進。

混合化從耗電量尤其大的CPU部分開始。最先得到應用的是美國英偉達在“Tegra 3”中采用的“4-PLUS-1”技術。這是在同一枚裸片上混載采用LP(低電力)工藝的低電力CPU內核和采用G(普通)工藝的主CPU內核群的做法,可根據負荷切換使用(圖9)。CPU內核采用相同的微架構。

圖9:利用不同的制造工藝安裝

區分使用CPU的英偉達在“Tegra3”中導入了可以區分使用以低電力工藝制造的CPU內核以及以普通工藝制造的CPU內核的“4-PLUS-1”技術。為了不使切換點附近頻繁發生切換,采取了預防措施。

“從決定切換到完成切換所需時間不到2ms,用戶應該注意不到”(英偉達日本技術營銷工程師Steven Zhang)。不過,如果負荷剛好在切換邊界附近變化,可能會頻繁進行切換處理,因此配備了在重復

移動電源相關文章:移動電源是什么

離子色譜儀相關文章:離子色譜儀原理

評論