松下32nm HKMG工藝分析出爐

日本松下公司曾表示其首款基于HKMG工藝的32nm芯片產品將于2010年的10月份上市。而經過長時間的等待之后,最近知名芯片技術分析公司 Chipworks的分析師Dick James終于發表了對松下這款32nm HKMG芯片產品的研究報告,報告稱該公司經過分析已經核實松下的這款32nm HKMG芯片產品采用的是gate first工藝制作。至于為什么號稱去年10月份已經上市,而到現在外界才拿到這款芯片進行分析,Dick James則解釋稱:“這款芯片產品確實如松下所承諾的那樣是在去年10月份即第44周上市的,不過由于產品流通環節繁瑣,因此我們到最近才得到了有關的實際產品。”

松下當年還曾經推出過基于HKMG工藝的45nm制程產品,當時其這款產品上市的時間和Intel的HKMG 45nm產品非常接近。不過在32nm節點,Dick James則表示,松下推出同類產品的步調則“要比Intel慢了一年左右,不過據我們所知,松下應該是首家開始批量生產32nm HKMG芯片產品的廠家。”

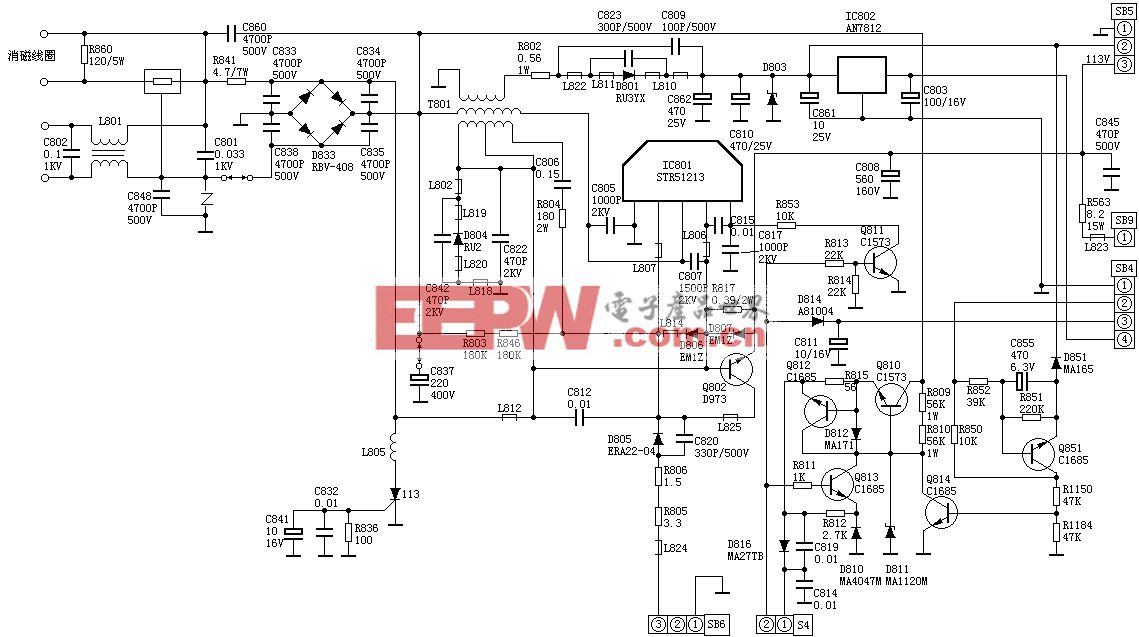

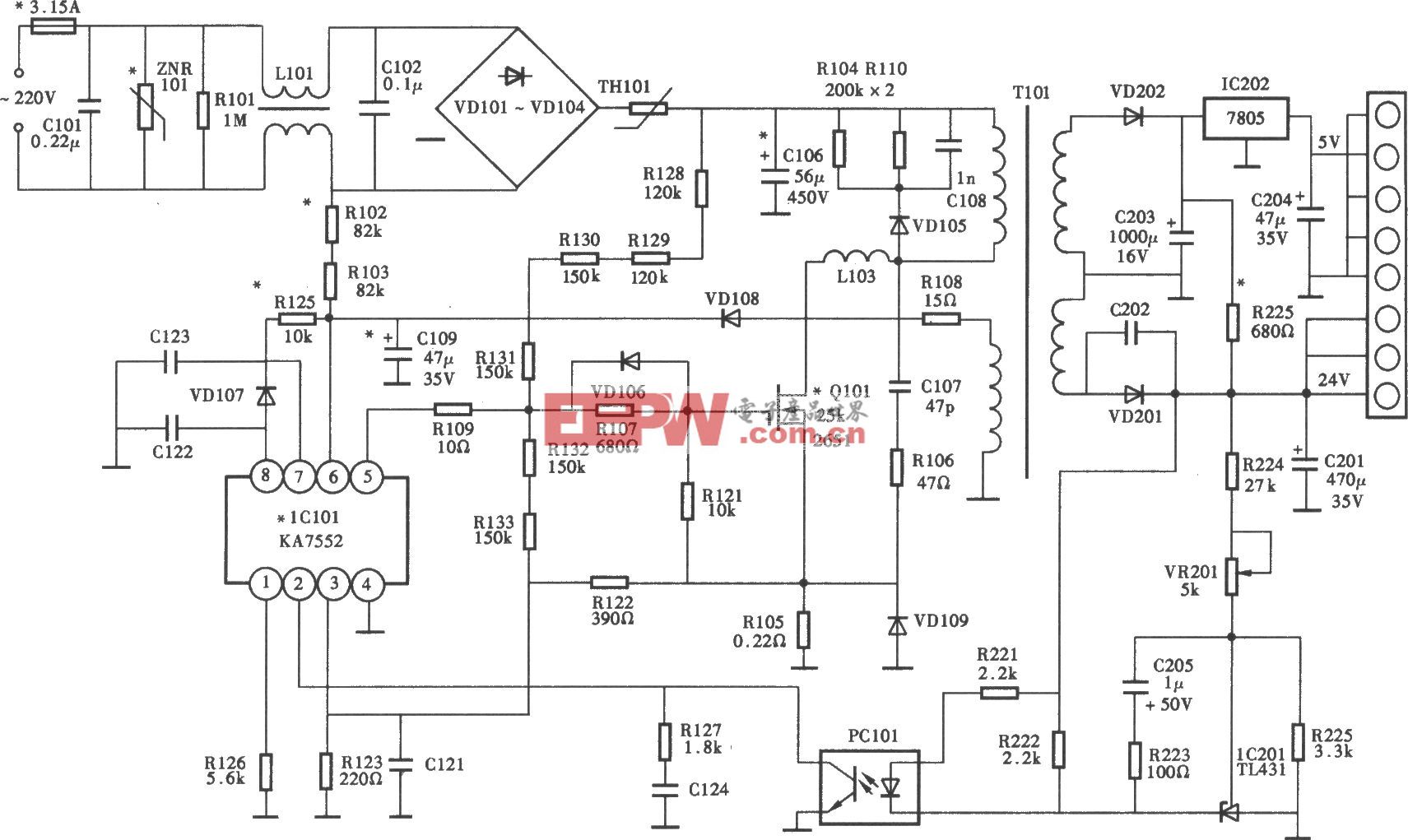

對松下32nm HKMG芯片產品的分析顯示,這款產品“采用九層金屬互連層設計(8層為銅互連,1層為鋁互連),互連層電介質則采用了low-k和extra-low-k兩種電介質混合的結構。芯片核心尺寸約45平方毫米,采用常規的FC-BGA封裝形式。最小的金屬觸點節距尺寸據松下公布的數據為120nm,不過我們在之前的分析中得出的實際節距尺寸則是125nm左右。”

松下還宣稱其32nm HKMG產品的性能提升了40%,同時功耗則減少了40%,芯片面積則縮小了30%。

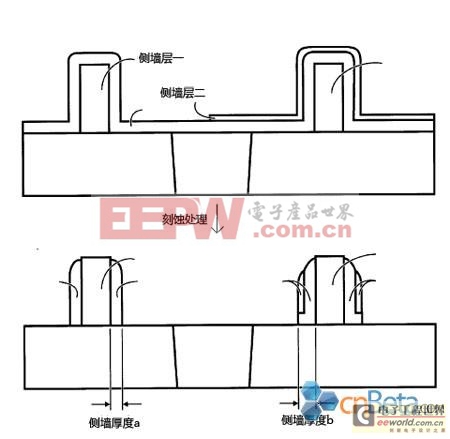

分析文章進一步指出:“可見松下32nm HKMG芯片的柵極采用多晶硅柵+底部TiN金屬功函數層的結構,在TiN層的底部可以觀察到high-k絕緣薄層結構。另外,值得注意的是這款產品的柵極采用了雙側墻工藝(dual-spacer),雙側墻工藝有時又被稱為差動式偏移隔離側墻(differential offset spacer)技術。另外在晶體管的漏源極頂部可觀察到一層薄薄的氮化物,這顯示松下這款產品的high-k絕緣層底部和硅溝道頂部之間可能采用了氮氧化物(推測應該是SiON)中間層。”

dual-spacer并不算是一項較新的技術,因此在近年的報道中較少被提及,這種技術的實質是通過調節側墻厚度來調整柵極的長度,從而控制漏源極擴散區和柵極的重合程度,以達到控制溝道有效長度,及減小漏源極與柵極的寄生電容的作用。

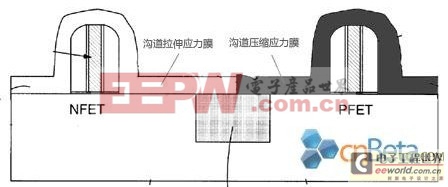

“柵極和漏源極的金屬化工藝(salicide)則采用常見的鎳金屬化摻雜鉑的工藝。不過松下32nm HKMG產品上產生應變力的機制則比較不明顯,他們采用的既不是基于柵極氮化層的技術,也不是嵌入式SiGe技術,另外也沒有使用雙應變力膜(dual-stress liner:即用兩層分別可對溝道施加拉伸應力和壓縮應力的氮化膜控制溝道應變力)技術。”

回顧松下當年的45nm HKMG工藝“似乎沒有使用任何溝道應變增強技術,PMOS溝道遷移率增強方面則只采用了100>晶向設計(普通芯片為110>晶向,但100>晶向的PMOS溝道空穴遷移率相對較高,當然晶向工程的效能與應變工程是無法相比的)。可見松下與Intel的45nm HKMG工藝其訴求的重點不同,Intel側重于晶體管性能的提升,而松下則側重于集成度的提高和成本的下降.而到32nm節點,松下的側重點又增加了high-k絕緣層的使用和由此帶來的低功耗/低漏電。”

評論