基于FPGA的多路模擬信號源設計與實現

0 引言

隨著遙測系統的不斷發展,系統復雜程度也隨之提高,因此在終端設計中,對信號源的頻率穩定度、幅值范圍和頻率范圍提出了越來越高的要求。這就要求遙測系統具備高碼速、實時可重構、處理復雜結構的能力,傳統的數字電路難以實現這些復雜功能。FPGA(現場可編程門陣列)是近幾年發展起來的硬件可編程芯片,具有硬件密度高、結構靈活、可編程、加密性強等良好性能,在高速信號處理領域占有至關重要的地位,也為多路模擬量信號源的實現,提供了有效的途徑。本文針對遙測應用,以大容量FPGA器件為核心,實現了電源獨立的不同頻率、不同波形的多路模擬量信號源。

1 系統硬件設計

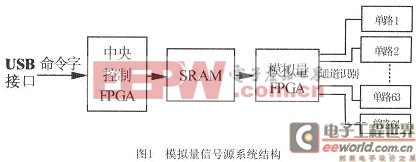

目前,大容量的FPGA主要有Altera、Xilinx、Lattice、Actel、Cypress等公司的產品。比較而言,Altera CycloneII系列FPGA芯片速度快、容量大、內嵌RAM多、并且有DSP硬件乘法器,是低成本、低功耗應用的最佳選擇。因此在本文中選用Altera公司的Cyclone II系列FPGA-EP2C8芯片,EP2C8芯片是1.25 V內核供電,具有8.256個邏輯單元(LE),36個M4K RAM塊,RAM總量為165,888,18個嵌入式乘法器以及208個管腳,其中包括182個最大可用I/O引腳。Altera公司有相應的開發軟件平臺Quartus II,此軟件功能強大,使用簡單,支持的器件種類眾多,可支持在線仿真,在線下載等,并具有豐富的IP核及邏輯功能模塊資源,便于使用VHDL+模塊/原理圖輸入界面等等。模擬量信號源主要包括中央控制FPGA單元、模擬量FPGA、靜態存儲SRAM、單路模擬量單元,如圖l所示,

整個系統使用USB 2.0接口與計算機進行通訊,信號由計算機軟件生成波形數據,通過USB口下載到主控FPGA,經過16位SRAM鎖存,將各路信號傳至模擬量FPGA,經由解碼分路選通,輸出電源獨立的不同頻率、不同波形的多路模擬量信號。其中包括4路單極性幅值O~30V,60路雙極性幅值±15V;四種波形分別為鋸齒波、正弦波和方波(占空比1:1),信號頻率為0~50Hz,以及固定電平,幅值可以初始設定,并可實現實時可調。

2 單路模擬量組成模塊設計

2.1 系統構成

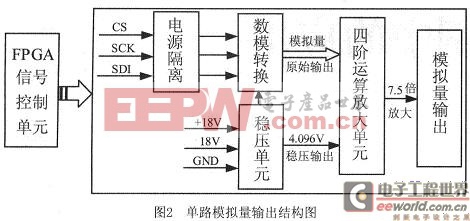

單路模擬量由電源隔離單元、前端穩壓單元、數模轉換(DAC)單元和運算放大單元等構成,具體構成如圖2所示,系統由雙18 V供電經過穩壓單元輸出4.096 V,給DAC和運放芯片提供工作電壓,另外通過指令啟動信號在SPI總線上發送FPGA的CS、SCK、SDI信號,傳至單路模擬量,將相應數字量進行D/A轉換,得到的模擬量數據經由運算放大輸出,即可實現64路模擬量波形。系統時鐘同步輸出,具有很高的可靠性。

評論