基于FPGA和SC16C554實現多串口通信的方法

0 引言

隨著電子技術的飛躍發展,通用數字信號處理器(DSP)的性能價格比不斷提高,數據處理能力不斷加強,其應用領域日益增多,在數據實時采集及高速數字信號處理中應用尤其廣泛。當DSP獨立構成一個處理單元時,往往需要和外設進行數據交換,其通信能力至關重要。在研制機載合成孔徑雷達系統時,信號處理機作為系統的核心要與飛控系統、穩定平臺、雷達信號源以及導航系統等部分進行數據交換;如何實現其與其它部分之間有效的通信成為系統設計的關鍵。串口通信因為其簡單,可靠仍然是廣泛采用的方法之一。

1 串口擴展方案選擇

多串口通信常用的實現方案有兩種:一種是軟件實現,采用軟件編程模擬串口,該方法成本低,但編程復雜、開發周期長、可靠性低。另一種是硬件實現,使用多串口單片機或專用串口擴展芯片,該方法雖然成本較高,但是開發比較簡單,可靠性高。

目前比較通用的實現方案是采用通用異步通信芯片實現串口擴展,采用FPGA/CPLD實現DSP與異步串口擴展芯片之間的邏輯控制,完全基于DSP接收和發送數據。該方案的缺點是:當數據量較大、多串口同時工作時占用DSP的時間較長,影響DSP的工作效率,且會造成數據丟失。因此本文提出了一種新的實現方法--基于FPGA和通用異步通信芯片實現多串口通信設計。在不進行硬件改動的基礎上,通過在FPGA內建立一個緩存機制,實現接收串口芯片的數據,達到一定量時向DSP發送中斷讀取數據。該設計能極大減少對DSP的占用時間,提高了DSP的工作效率;同時提高了對串口芯片中斷請求的響應速度,解決了數據丟失的問題。

2 硬件電路設計

本設計采用通用異步通信芯片SC16C554來實現串口擴展。SC16C554主要特點有:

1.有A、B、C、D四個通道獨立收發數據;

2.最高傳輸速率可達5Mbit/s,具有可編程波特率發生器,便于靈活選擇數據收發頻率;

3.具有16字節的收發FIFO,且有1、4、8、14字節四個可選擇的中斷觸發深度;

4.可通過編程設置傳輸數據的格式(數據長度,校驗位,停止位);

5.具有可獨立控制的發送、接收、線路狀態和MODEM狀態中斷;

6.充分分級的中斷系統控制,全面的線路狀態報告功能。

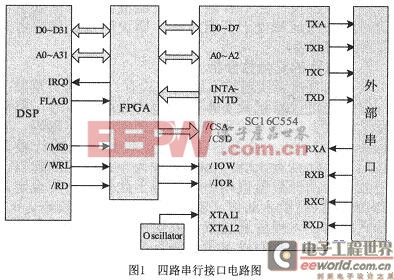

基于FPGA和SC16C554實現多串口通信的基本原理圖如圖1所示:

3 軟件設計及實現

系統實際工作所需波特率分別為9600、38400、115200、153600 。分析計算可得不同波特率發送數據時,連續兩個數據之間的時間間隔如表1所示:

由表1可知單個通道連續兩個中斷產生的最小時間間隔為65μs;因此在65μs的時間內如果可以實現對四個通道分別進行一次讀數據操作,即使是四個通道同時來數據也不會發生數據丟失的現象。

3.1 數據的存儲設計

即在FPGA內部建立一個緩存機制。設計采用在FPGA內部做一個雙端口RAM(DPRAM),用來存儲串口數據,DSP通過訪問DPRAM得到接收的串口數據。

DPRAM指一個存儲模塊卻包含兩個獨立的端口,這兩個端口共用同一塊地址空間,兩個端口都可以向這塊空間里寫數據或從中讀取數據。DPRAM的讀寫數據的模式包括只讀、只寫、讀寫三種模式,其中讀寫模式又包括先寫后讀、先讀后寫、只寫不讀三種模式,我們采用先讀后寫的模式。

我們將DPRAM的地址空間分為四部分,分別用來存放四個通道的數據。當FPGA收到數據時,我們可以根據置通道標志寄存器CS[2:0]的值來判斷該數據來自哪個通道,將其存入對應的地址空間,并將該通道對應地址線加一。當該通道存儲數據量達到編程設置的觸發深度時,就將DSP中斷寄存器dspint置低,向DSP發送中斷;同時向DPRAM內一事先定義好的公共存儲空間寫入通道標志字。當DSP收到中斷后,首先訪問該公共存儲區讀取通道標志字,判斷該中斷是由哪個通道產生的;然后調用相應的接收函數從DPRAM內讀取該通道的數據存入指定的地址空間等待處理。

合成孔徑雷達相關文章:合成孔徑雷達原理

評論