基于FPGA技術的模擬雷達信號的設計與實現

前言

FPGA(現場可編程門陣列)是由掩膜可編程門陣列和PLD(可編程邏輯器件)演變而來的,并將二者的特性結合在一起,使FPGA既有掩膜可編程門陣列的高邏輯密度和通用性,又有PLD的可編程特性。FPAG技術的發展使得單個芯片上集成的邏輯門數越來越多,能實現的功能越來越復雜。它以編程方便、集成度高、速度快等特點受到電子設計人員的青睞。人們可以通過硬件編程的方法設計和開發ASIC(專用集成電路)芯片,極大地提高芯片的研制效率、降低開發費用。

通過應用FPGA技術,較好地為“某型雷達告警設備”的配套檢測儀器實現了模擬雷達信號發生器ASIC芯片的設計,該芯片能夠提供“某型雷達告警設備”測試過程中所需的多種典型的重頻脈沖及制導信號等,其中包括SA-6重頻信號、SA-2重頻脈沖及制導信號、SA-3重頻脈沖及制導信號、雷達脈沖視頻等。所設計的ASIC芯片的性能較為理想。

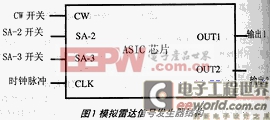

模擬雷達信號發生器的結構

模擬雷達信號發生器的結構如圖1所示。可以看到,模擬雷達信號發生器由連續波雷達模擬信號CW開關、制導信號SA-2開關、制導信號SA-3開關、時鐘脈沖產生器、輸出1、輸出2和產生模擬雷達信號的控制芯片組成。上述開關都是高電平有效,開關的消抖動電路放在控制芯片部分考慮。時鐘脈沖產生器由外部的晶體振蕩器產生一個頻率穩定的1MHz時鐘脈沖,用來滿足信號脈沖寬度的要求。“CW開關”有效時,“輸出2”輸出連續波雷達達模擬信號;“SA-2開關” 有效時,“輸出2”輸出SA-2的重頻脈沖,“頻脈沖,“輸出1”輸出SA-2的指令信號組;“SA-3開關”有效時,“輸出2”輸出SA-3的重頻脈沖,“輸出1”輸出SA-3的指令信號。

ASIC芯片的設計

1芯片主要性能指標

(1)產生連續波雷達模擬信號:重頻3012Hz,脈寬1μs±0.1μs;

(2)產生制導信號SA-2重頻脈沖:重頻2463Hz,脈寬0.5μs±0.1μs;SA-2指令信號組:重頻2463Hz,每秒132個單指令,44個指令組,指令脈寬1μs±0.1μs;

(3)產生制導信號SA-3重頻脈沖:重頻3497Hz,脈寬0.5μs±0.1μs;SA-3指令信號同SA-3重頻脈沖等。

芯片的輸出和輸出信號定義如下:

輸入信號:連續波雷達模擬信號輸入;制導SA-2輸入;制導SA-3輸入;時鐘脈沖輸入等。

輸出信號:輸出1;輸出2。

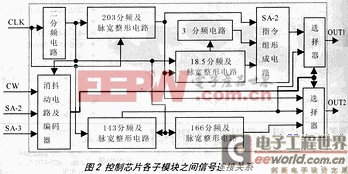

2芯片結構

該芯片分為10個子模塊,如圖2所示。各子模塊的作用如下:

二分頻電路

時鐘脈沖輸入CLK頻率為1MHz,一方面為203分頻及脈寬整形電路、143分頻及脈寬整形電路提供1μs的方波,使二個脈寬整形電路產生0.5μs脈寬信號;另一方面CLK經二分頻電路產生500kHz信號,提供給203分頻及脈寬整形電路、143分頻及脈寬整形電路、166分頻及脈寬整形電路作為分頻電路的輸入信號,同時提供給消抖動電路及編碼器、166分頻及脈寬整形電路、18.5分頻及脈寬整形電路用來產生1μs脈寬信號。

消抖動電路及編碼器

消抖動電路能消除開關的(文內未見有提及機械開關,如電路開關應是上升、下降邊沿抖動對輸出的影響,它分別將開關的輸入信號轉變為1μs脈寬的輸出信號。CW開關、SA-2開關、SA-3開關信號經編碼后產生對應的碼元00、01、10信號,控制選擇器工作。

各分頻及脈寬整形電路

5個分頻電路按功能的要求產生各自的重頻頻率,再經脈寬整形電路產生出符號各信號脈沖寬度(1μs或0.5μs)的脈沖。如:203分頻及脈寬整形電路產生2463Hz、0.5μs脈寬的信號;166分頻及脈寬整形電路產生3012Hz、1μs脈寬的信號;143分頻及脈寬整形電路產生3097Hz、 0.5μs脈寬的信號;18.5分頻及脈寬整形電路產生132Hz、1μs脈寬的信號;3分頻電路產生44Hz方波信號。

SA-2指令組形成電路

將2463Hz、132Hz與44Hz信號一起加到SA-2指令組成電路,產生一組脈沖序列,構成每秒132個單指令、44個指令組。在560μs內只有一個脈沖,稱為單指令,有2個或更多脈沖,稱為指令組。

選擇器

依據編碼器輸送來的碼元,選擇器輸出對應的工作狀態。當碼元為“00”時,“OUT2”輸出連續波雷達模擬信號;碼元為“01”時,“OUT2”輸出SA -2的重頻脈沖,“OUT1”輸出SA-2的指令信號組;當碼元為“10”時,“OUT2”輸出SA-3的重頻脈沖,“OUT1”輸出SA-3的指令信號。

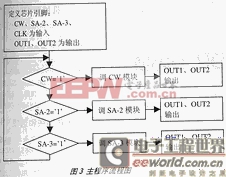

3控制芯片VHDL語言描述

由芯片的結構可以看出,6個分頻器電路除了它們的分頻系數不同外,VHDL(甚高速集成電路描述語言)的結構是類似的,稍加改變便可設計成各自獨立的元件單元。脈寬整形電路可設計成標準的基本單元,以元件形成供4個脈寬整形電路和消抖動電路調用。SA-2指令組形成電路、編碼器和選擇器分別設計成獨立的元件單元。將上述各單元按它們的信號關系連接起來,便構成了芯片構造體描述。該設計直接采用VHDL的RTL(寄存器傳輸描述)方式,來簡化設計步驟和縮短設計時間。其VHDL硬件描述語言主程序流程圖如圖3所示。

結束語

我們采用VHDL硬件描述語言,通過MAX+PLUS Ⅱ開發平臺,經編譯、仿真無誤后,寫入Altera公司EPM7064S器件中,經調試,其性能完全達到設計要求。

評論