以FPGA為橋梁的FIFO設計方案及其應用

引 言

在利用DSP實現視頻實時跟蹤時,需要進行大量高速的圖像采集。而DSP本身自帶的FIFO并不足以支持系統中大量數據的暫時存儲,這就要求大的中間緩存,而專用的高速FIFO芯片價格昂貴且容量受限,大大增加了商業成本,因此在實際應用中尋找FIFO代替器件是很有必要的。

1 器件選擇

這里在視頻信號處理系統中,將利用FPGA作為橋梁,實現對SDRAM的控制,以達到大量高速存取數據的功能。之所以選取SDRAM,主要是因為在各種隨機存取器件中,SDRAM的容量較大,價格較低,且數據突發傳輸模式大大提高了存取速度,能夠滿足應用的要求。

FIFO的速度受到兩個因素的限制:

(1)SDRAM的最高工作頻率。SDRAM的工作頻率越高,數據的傳輸速率就越高;

(2)SDRAM的突發長度。SDRAM的突發長度越長,對數據流的吞吐量就越大,可以從某種程度上提高數據的傳輸速率。

FIFO的大小由所選SDRAM芯片的容量來決定。該設計以采用MICRON公司的MT48LC4M3282(4 BANK×4M×32 b)為例,存儲容量為128 Mb,數據帶寬為32位,內部由4個BANK組成,每個BANK有4 096行和256列。

MT48LC4M3282的控制信號有CLK(時鐘信號)、CKE(時鐘使能)、CS(片選信號)、WE(寫使能)、CAS(列有效)、RAS(行有效)、DQM0~DQM3(輸入輸出使能)。控制信號組成的常用控制命令如表1所示。

2 FIFO系統設計

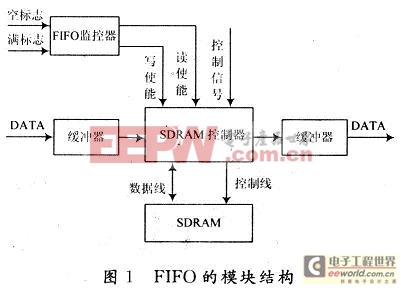

FIFO系統由FGPA和SDRAM兩部分組成。其中,FGPA內部包含FIFO監控器、緩沖器、SDRAM控制器三個模塊。FIFO監控器的作用是將FIFO的狀態轉變成狀態機的讀、寫信號。若操作為向SDRAM寫數據,則在FIFO已滿時,FIFO監控器送出一個信號,以阻止寫操作繼續向FIFO中寫數據而造成溢出;若操作為向SDRAM讀數據,則在緩沖器已空時,FIFO監控器送出一個信號,以阻止讀操作繼續從FIFO中讀數據而造成無效數據的讀出。FIFO的模塊結構如圖1所示。

評論