理解FPGA中的壓穩態及計算壓穩態的方法

本白皮書介紹FPGA 中的壓穩態,為什么會出現這一現象,它是怎樣導致設計失敗的。介紹怎樣計算壓穩態MTBF,重點是對結果造成影響的各種器件和設計參數。

引言

當信號在不相關或者異步時鐘域之間傳送時,會出現壓穩態,它是導致包括FPGA 在內的數字器件系統失敗的一種現象。本白皮書介紹FPGA 中的壓穩態,解釋為什么會出現這一現象,討論它是怎樣導致設計失敗的。

通過計算壓穩態導致的平均故障間隔時間(MTBF),設計人員知道是否應采取措施來降低這類失敗的概率。

本白皮書解釋怎樣利用各種設計和器件參數來計算MTBF, FPGA 供應商和設計人員怎樣提高MTBF。可以通過設計方法和優化措施來降低出現壓穩態失敗的概率,從而提高系統可靠性。

什么是壓穩態?

FPGA 等數字器件中的所有寄存器都有確定的信號時序要求,使每一個寄存器能夠正確的采集輸入數據,產生輸出信號。為保證能夠可靠的工作,寄存器輸入必須在時鐘沿之前穩定一段時間( 寄存器建立時間,即tSU),在時鐘沿之后也要保持穩定一段時間( 寄存器保持時間,即tH)。一定的時鐘至輸出延時 (tCO) 之后,寄存器輸出有效。如果信號轉換不能滿足寄存器的tSU 或者tH 要求,寄存器輸出就有可能進入壓穩態。在壓穩態中,寄存器輸出在高電平和低電平狀態之間徘徊一段時間,這意味著,輸出延時超出設定的tCO 之后才能轉換到確定的高電平或者低電平狀態。

在同步系統中,輸入信號必須滿足寄存器時序要求,因此,不會出現壓穩態。信號在不相關或者異步時鐘域電路之間傳輸時,一般會出現壓穩態問題。在這種情況下,由于信號可能在相對于目的時鐘的任意時間到達,因此,設計人員不能保證信號能夠滿足tSU 和tH 要求。然而,并不是所有不能滿足寄存器tSU 或者tH的信號轉換都導致壓穩態輸出。寄存器是否會進入壓穩態以及返回穩定狀態所需要的時間與器件制造工藝以及實際工作條件有關。在大部分情況下,寄存器會很快返回穩定狀態。

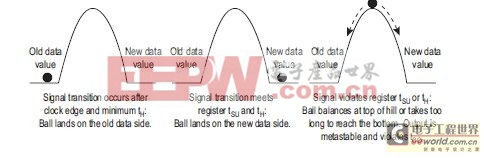

可以把寄存器在時鐘邊沿采樣數據信號形象的看成是球從山上滾落下來,如圖1 所示。山的兩邊代表穩定狀態——信號轉換之后,信號的老數據和新數據,山頂代表壓穩態。如果球從山頂滾落,它會處于不確定狀態,實際中,它稍偏向一側,然后,落到山下。從山頂開始,越到山腳,球到達底部穩定狀態的速度越快。

圖 1. 利用球從山上落下描述壓穩態

如果數據信號在時鐘沿之后以最小的 tH 轉換,這就類似球從山的“老數據值”一側落下,輸出信號保持在該時鐘轉換的最初值不變。當寄存器數據輸入在時鐘沿之前以最小 tSU 轉換,保持時間大于最小 tH,這就類似球從山的“新數據值”一側落下,輸出信號很快達到穩定的新狀態,滿足確定的tCO 時間要求。但是,當寄存器數據輸入不能滿足tSU 或者 tH, 時,這就類似于球從山頂落下。如果球落在山頂附近,那么,它會花很長時間才能落到山腳,增加了時鐘轉換到穩定輸出的延時,超出了要求的tCO。

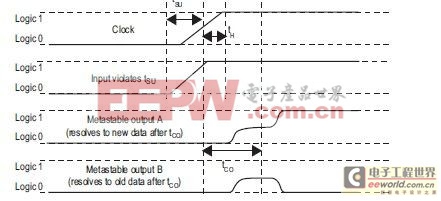

圖2 描述了壓穩態信號。時鐘信號轉換時,輸入信號從低電平狀態轉換到高電平狀態,不能滿足寄存器的tSU 要求。數據輸出信號從低電平狀態開始,進入壓穩態,在高電平和低電平狀態之間徘徊。信號輸出A 轉換到輸入數據的新邏輯1 狀態,輸出B 返回到數據輸入最初的邏輯0 狀態。在這兩種情況下,輸出轉換到確定的1 或者0 狀態的時間被延遲了,超出了寄存器要求的tCO。

圖 2. 壓穩態輸出信號實例

評論