基于CPCI體系的高性能監測測向處理平臺研究

摘 要: 提出一種新的高速并行采樣技術架構以及基于可編程芯片技術和支持靈活配置的并行處理嵌入式硬件架構。該平臺集多通道高速采集、大容量數據存儲、高性能DSP與大規模FPGA緊耦合實時處理等功能于一體,在綜合集成與應用方面具有創新性,能夠保障對多模式、多速率、多頻段信號分析在信號層上頻域的寬闊全覆蓋和時域的連續性,同時又因其硬件上提供了豐富的資源裕量,因而可以滿足信息層上對多種標準和協議分析的需求及應對其未來的演進。

為了克服傳統監測測向處理系統通用性和擴展性差的缺點[1],本文依托軟件無線電技術[2],對一體化設計所需的高速實時數據采集以及高速實時分析處理所需的終端處理硬件結構進行了深入闡述。該系統能夠滿足目前新體制和復雜信號環境下的監測測向設備各項指標要求,在有效節約資源和成本的同時,擁有較高水平的多系統集成效能。在研究過程中,本文綜合考慮目前數字處理終端與不同類型CPU(主機)的接口與結構關系的優缺點,最終選擇了基于Compact PCI體系的高性能監測測向處理平臺設計方案。

1 系統結構

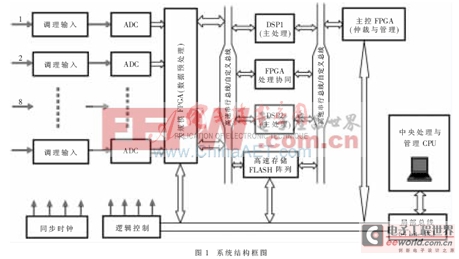

本文所述的平臺結構具有靈活性和開放性的特點,其主要工作原理為:大規模FPGA用于接收多通道高速采樣數據流,完成必要的預處理;主控FPGA依據每路信號的處理要求仲裁各路FPGA/DSP的片選信號,同步啟動進行實時處理;多片實時處理DSP和主控FPGA緊耦合構成并行處理系統的核心;最后通過局部總線接口送入中央處理CPU作進一步分析處理,完成信息的綜合存儲管理等[3]。系統結構框圖如圖1所示。

2 具體方案

2.1 高速數據采集

高速數據采集是高性能監測測向處理平臺研究[4]的首要問題。其設計與實現,一方面由需求引導,另一方面也要求對系統各個環節有整體的把握。合理設計模擬信號調理電路、高穩時鐘產生電路、高速數據流傳輸路徑、合理的時序及控制邏輯,并充分考慮信號完整性和電磁兼容等問題,是設計一個高性能數據采集模塊的基本保障。

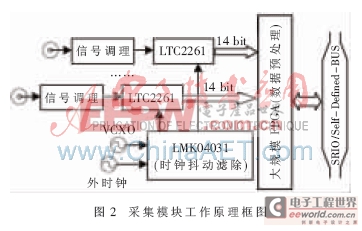

對于本文所關注的高速數據采集而言,若直接采用滿足采樣率設計要求的單片ADC芯片實現,會帶來動態范圍不夠、缺乏靈活性和成本較高、風險較大等問題。而如果選擇采用多片采樣率較低的芯片用交替采樣的方法來實現高速采樣的方案,則電路較復雜,而且多片ADC之間延時的不一致和增益的不匹配會使采樣后的信號難以無失真的復合。鑒于此,本文所述的高速數據采集設計思路是:模塊化設計具有適當采樣率的A/D板,基于頻帶分割和精確同步觸發的寬帶、大動態數據采集方案。本技術架構在硬件設計上具有模塊化、可擴展的特色,在性能上具有等效采樣率高及采樣帶寬不受ADC及調理電路限制的優點。采集模塊工作原理如圖2所示。

評論