新出現的SoC FPGA上的策略考慮

這一關鍵點的主要推動因素包括:過渡到并行和多核處理,以提高功效;FPGA成為前沿的新半導體工藝技術;嵌入式系統中越來越多的使用了FPGA;摩爾定律的經濟現實;CPU在體系結構上的增強。

隨著SoC FPGA時代的來臨,系統設計人員在選擇這些器件時需要考慮以下關鍵策略問題:

·哪些器件會經歷“平臺效應”,使得供應商、輔助支撐系統以及用戶之間出現“自我增強循環”?

·哪些器件能夠在多種選擇中支持IP重用 ?

·哪些FPGA技術能夠最大限度的降低成本,提高性能 ?

SoC FPGA的關鍵點

業界集成FPGA和CPU系統在第一個十年發展中既有成功也有失敗。最初的SoC FPGA在商業上并不是很成功,而 FPGA中的軟核 CPU得到了廣泛應用,這表明市場對FPGA和CPU技術集成有基本的需求。各種新的因素改變了業界環境,導致關鍵點的出現,SoC FPGA將在市場上獲得非常廣泛的應用。

推動業界這一關鍵點出現的關鍵因素包括: 計算功效 、FPGA過渡到前沿工藝技術 、FPGA在嵌入式系統中的應用、摩爾定律的經濟現實 、CPU在體系結構上的增強。

計算功效

計算的發展趨勢是并行處理,近期集中在處理器從高成本的單核處理發展到多核實現上。在提高計算性能的同時降低功耗,這促使人們采用FPGA邏輯作為CPU的硬件加速器。

一個 SoC FPGA系統提高了功效,實現了靈活的軟件劃分。SoC FPGA支持數百路數據信號連接不同的功能區,實現每秒100-gigabits (Gbps)帶寬,甚至更大的帶寬,其延時在納秒級,性能和延時比分立器件要高幾個數量級。而且,單個集成平臺支持存儲器控制器的共享,寬帶存儲器可以訪問硬件加速器。

性能的提高以及存儲器訪問功能支持采用 FPGA來實現功能更強的加速器,以滿足各種各樣的計算要求。由于硬件加速器在功效上要比 CPU高 1,000多倍,因此,與簡單的多核并行方法相比,采用 SoC FPGA進行設計是實現高功效計算較好的方法。

FPGA過渡到前沿工藝技術

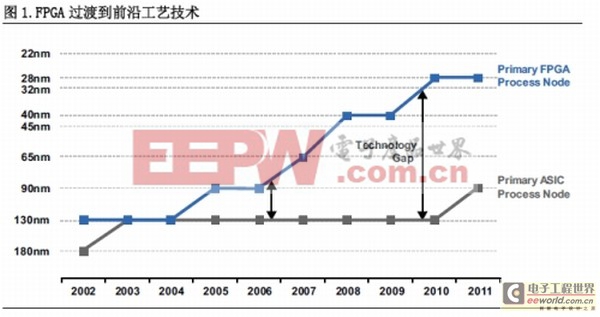

在 2000年,最新的 FPGA采用了 130-nm工藝技術進行開發,而目前的 CPU采用的是90-nm工藝技術。由于有更高級的 CPU,因此,第一代 SoC FPGA的推出有些滯后。然而,當今的前沿 FPGA采用 28-nm工藝技術,相對而言只有很少的商用 CPU或者ASSP使用了這一工藝技術,當然在今后有可能使用該技術。FPGA在工藝技術上的優勢明顯增強了這些集成器件的市場潛力,供應商也傾向于在這方面加大投入,這是因為設計人員不需要在 CPU性能上作出犧牲,如圖1所示。

評論