IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

摘 要:本文介紹了一種采用級聯結構在FPGA上實現任意階IIR數字濾波器的方法。此設計擴展性好,便于調節濾波器的性能,可以根據不同的要求在不同規模的FPGA上加以實現。

IIR數字濾波器在很多領域中有著廣闊的應用。與FIR數字濾波器相比,它可以用較低的階數獲得高選擇性,所用存儲單元少,經濟而效率高,在相同門級規模和相同時鐘速度下可以提供更好的帶外衰減特性。下面介紹一種在FPGA上實現IIR數字濾波器的方法。

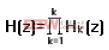

IIR數字濾波器的結構 任意階的IIR濾波器可通過數學分解,表示為:

其中為如下的二階形式:

這樣就可以將任意階的IIR濾波器通過若干二階網絡(也稱為濾波器的二階基本節)級聯起來構成,其結構如圖1所示。其中,代表第i級的二階網絡。

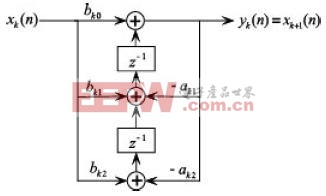

對于每一個二階基本節,可以轉置直接II型結構加以實現,如圖2所示。

采用這種級聯結構實現IIR濾波器的優點是每一個基本節只是關系到濾波器的某一對極點和一對零點,調整系數a0i、a1i、a2i,只單獨地調整了濾波器第i對零點而不影響其他任何零、極點。同樣,調整b1i、b2i系數、也只單獨調整了第i對極點。因此,這種結構便于準確地實現濾波器的零、極點,也便于調整濾波器的頻率響應性能。這種結構的另一個優點是存儲單元需要較少,在硬件實現時,可以用一個二階節進行時分復用,從而降低對FPGA硬件資源的要求。

評論