高效FIR濾波器的設計與仿真-基于FPGA

摘要:該文在介紹有限沖激響應(FIR)數字濾波器理論及常見實現方法的基礎上,提出了一種基于FPGA的高效實現方案。該方案采用對稱結構、加法和移位代替乘法運算、優化的CSD編碼、流水線和級聯技術等方面對傳統的設計方法進行了改進,并借助FPGA濾波器芯片和Quartus II軟件、Matlab軟件對該方案進行了仿真驗證。仿真實驗結果表明:此種FIR濾波器的實現方法運算速度快、實時性好、節省硬件資源,其性能優于傳統的FIR濾波器設計方法。

隨著信息時代和數字世界的到來,數字信號處理已成為當今一門極其重要的學科。作為數字信號處理分支之一的數字濾波器,也受到了人們越來越多的關注。它是通信、語音、圖像、自動控制、雷達、航空航天、醫療等領域中的一種基本處理部件,具有穩定性好、精度高、靈活性大等突出優點。

數字濾波器包括有限沖激響應(Finite impulse response,簡稱FIR)濾波器和無限沖激響應(Infinite impulse response,簡稱IIR)濾波器兩大類,其中的FIR濾波器因可以得到嚴格的線性相位、有限精度的計算不會產生振蕩、運算速度快等優點受到了人們更多的青睞。在非實時或低速系統中,FIR算法可以在DSP或CPU上用軟件實現,但是在一些實時性要求較高的系統(如雷達控制、無線通訊系統等)中,由于受到乘法器和加法器電路的限制,該實現方法則不能滿足速度的要求。近幾年來,隨著微電子技術與工藝的迅猛發展,現場可編程門陣列(Field programmable gate array,簡稱FPGA)以其可編程性、低成本性、高邏輯密度和高可靠性,得到了越來越廣泛的應用。本文借助Ahera公司的FPGA芯片和Quartus II軟件、Matlab軟件,介紹了一種高效FIR濾波器的設計與實現方案。

1 基于FPGA的高效FIR濾波器的設計思路

一個Ⅳ階的FIR數字濾波器可由差分方程

或轉移函數:

來描述。式中: x(n)是濾波器的輸入信號,y(n)是濾波器的輸出信號,h(n)是濾波器系數。從以上的表達形式可以看出,FIR濾波器是通過加法器、移位器和乘法器組合而實現的,乘法器和加法器的效率及速度等特性對整個濾波器的性能起著決定性的作用。

1.1 采用對稱結構

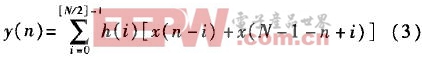

在很多應用場合,濾波器都是線性時間不變量(Linear time-invariant,簡稱LTI)濾波器,也就是帶有常系數的濾波器。對于具有線性相位的FIR濾波器,其輸出表達式(1)變成了如下的形式:

由此可見,利用它的對稱形式比直接實現少用了一倍的乘法器,大大節省了硬件資源,而且可以提高速度。

1.2 用加法和移位代替乘法運算

乘法器是FIR濾波器中比較重要的部件,它的結構直接影響了濾波器的性能。傳統的濾波器中的乘法器采用BOOTH乘法器結構,它主要

包括3個模塊:BOOTH編碼、部分積加法器陣列及進位加法器。在這種結構中,隨著濾波器的階數的增加,電路的規模勢必迅速增加。

因為在實際應用的大多數情況下,濾波器的系數是固定的值,所以濾波器中所有的乘法都是固定系數乘法。實現固定系數乘法的一種常用方法是用移位和加法運算來代替并行乘法。這樣一方面可以提高硬件實現的速度,另一方面可以減少所需的硬件資源。

1.3 采用優化的CSD編碼

眾所周知,二進制數在實現乘法或加法時,數值為0的位是不參與運算的。因此,對輸入信號進行編碼時,如果能使0位的數量最多,則完成相應的運算所需要的硬件將會大大減少,運算的速度也會相應地提高很多。正則有符號數字量(Canonic signed digit,簡稱CSD)正是基于此思想而提出來的一種新型編碼方法,它是具有最少非0元素的表示法。

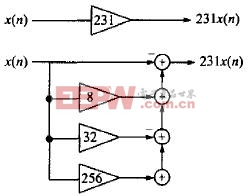

CSD碼的特性是最終表達式在兩個數位之間至少有一個0。它的算法是從最低有效位開始,用10…01取代所有大于2的一序列,用1101

取代1011;然后從最高有效位開始,用011代替101。例如十進制數231的CSD碼為100101001,可以看出,在實現其乘法時,只需要4個加法器(如圖1所示)。若采用普通的二進制代碼實現,因(231)10=(11100111)2,需要5個加法器。可見,采用CSD碼節省了加法器的數量。

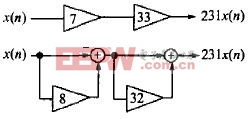

為了進一步提高效率,對于某些數據,還可以采用優化的CSD編碼,即首先將系數拆分成幾個因子,再實現每一個因子。如對231,首先拆分成7×33,然后分別實現因子7和33。7和33每個因子都只需要1個加法器(如圖2所示),即實現231的乘法時只需要2個加法器,因此效率得到了更大的提高。

圖1 231的CSD碼的實現

圖2 231的優化CSD碼的實現

1.4 采用流水線技術

在濾波器的加法運算中,根據內部的數據流規則,可以采用流水線技術將一個運算操作分解成一些小規模的基本操作,將進位和中間值存儲在寄存器中,并在下一個時鐘周期內繼續運算。對于FPGA器件來說,采用流水線式的設計,可以在不增加電路成本和規模的基礎上提高運算處理的實時性。

1.5 采用級聯技術

設計高階的濾波器時,可以采用多個低階濾波器級聯而成,如n個10階的FIR濾波器可以級聯成一個10n階的濾波器,級聯后的濾波器可以

是對稱的,也可以是非對稱的。實踐證明,采用分布式算法,級聯后的濾波器不會因為長度的增加而使性能明顯下降。

評論