基于FPGA的數字核脈沖分析器硬件設計方案

3.3 接口電路設計

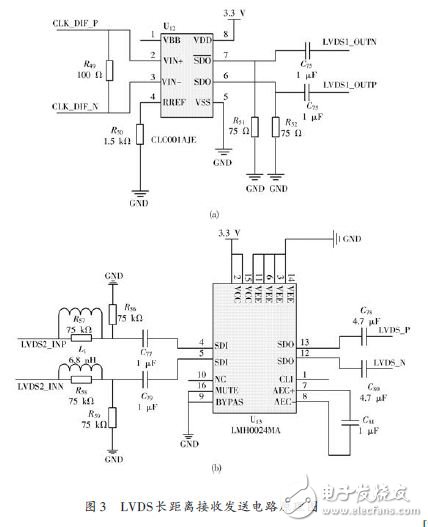

本文引用地址:http://www.j9360.com/article/221558.htm接口電路設計采用了LVDS和RS485兩種長距離數據傳輸接口,用于實現核能譜數據的遠程傳輸。LVDS即低電壓差分信號,是一種可以實現點對點或一點 對多點的連接,具有低功耗,低誤碼率,低串擾,低噪聲和低輻射等特點。LVDS在對信號完整性、地抖動及共模特性要求較高的系統中得到了越來越廣泛的應 用。圖3為低電壓、最高數據傳輸速率為655 Mb/s 的LVDS 接口電路。

在高速通信狀態下,其通信距離可達到幾百米。

而RS 485接口采用平衡驅動器和差分接收器的組合,有很強的抗共模干擾能力和抗噪聲干擾能力。其最大的通信距離約為1 219 m,最大傳輸速度為10 Mb/s,傳輸速率與傳輸距離成反比,在100 Kb/s以下的傳輸速率下,可以達到最大的通信距離。

3.4 電源電路

穩壓電源通常有兩類:線性穩壓電源和開關穩壓電源。開關電源的功率調整開關晶體管工作在開關狀態,極易產生嚴重的開關干擾,若采用開關穩壓電源,這些干擾將嚴重地影響數字多道分析器的正常工作,降低A/D轉換精度。所以本文采用線性穩壓電源為各功能模塊供電。線性穩壓電源的優點是輸出電壓比輸入電壓低,反應速度快,輸出波紋較小,工作產生的噪聲低。

本文設計的電源電路其輸入電壓為9~12 V,輸出電壓有5 V,3.3 V,2.5 V,1.8 V,1.2 V.線性穩壓電路為單端轉差分、ADC、FPGA、LVDS等各模塊供電。

4 數字尋峰

NaI(Tl)探測器輸出信號通過調理電路后進入高速ADC,ADC 進行連續高速的采樣,然后由FPGA 完成數字核脈沖信號的積分、峰值檢測、閾值判斷等功能[8]。由于當核能譜達到峰值時,其一階導數為0,據此可在連續的輸入信號中找到各核脈沖的峰值,并 將該峰值對應道址的計數值加1,從而形成核能譜。為提高尋峰效率,尋峰之前需要對離散脈沖信號進行閾值判斷,對幅值低于閾值下限的信號不進行尋峰處理,可 大大減少參與尋峰的離散核脈沖信號。

5 功能測試

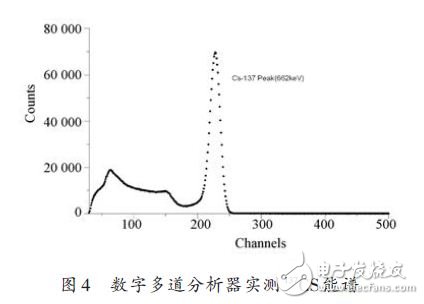

利用Borland C++集成開發環境開發了譜數據處理上位機軟件,軟件實現了能譜顯示、能譜數據管理、系統參數設置、RS 485通信等功能。圖4是本文設計的數字多道分析器分析137CS得到的1 024道能譜,其能量分辨率接近8%.

6 結語

本文提出了一種基于FPGA的數字核脈沖分析器硬件設計方案。該方案在單片FPGA中實現了多道脈 沖幅度的數字分析功能,通過軟件功能仿真和實際運行,說明了數字多道脈沖幅度分析器硬件設計的可行性,將FPGA 應用到數字能譜測量系統能充分發揮其并行處理優勢,并能有效降低硬件電路設計的復雜度。

fpga相關文章:fpga是什么

評論