基于ARM和FPGA的便攜人工地震數據采集系統設計

近年來,隨著可編程邏輯器件(CPLD/FPGA)的迅猛發展,可編程邏輯器件在數據采集、邏輯接口設計、電平接口轉換和高性能數字信號處理等領域取得越來越廣泛的應用。CPLD/FPGAD不僅可以解決電子系統小型化、低功耗、高可靠性等問題,而且開發周期短、投入少,同時不斷下降的芯片價格極大推動了CPLD/FPGA器件在廣泛應用領域的使用。本文介紹一種ARM微處理器+FPGA的硬件設計,融合嵌入式Linux技術,實現一種小型化、移動性強、網絡耦合度高的便攜式人工地震數據采集系統。該系統以滿足人工地震觀測的需要、減小儀器尺寸和重量、降低功耗、降低野外工作強度和提高數據采集工作效率為目標。

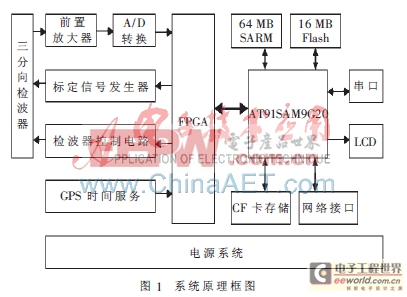

1 系統硬件設計

采集系統由CPU核心板、A/D數據采集板和電源板組成,系統原理如圖1所示。CPU板以Atmel AT91SAM9G20微處理器為核心,通過總線和GPIO分別與64 MB SDRAM、16 MB Norflas和FPGA A3P250接口。板上大容量CF卡安裝有FAT文件系統,用于地震波形數據的本地存儲。網絡接口提供遠程登錄、數據傳輸及系統控制功能,包括實時數據流傳輸。LCD屏顯示系統工作參數,如溫度、經緯度、高程、系統網絡IP地址等信息。串口用于輸出調試信息,也被SAM-BA軟件用來下載燒寫引導加載程序U-boot和嵌入式Linux操作系統內核映像文件。A/D采集板上有三路模數轉換數據采集通道,標定信號發生器和檢波器控制信號調理電路。高效的電源轉換電路是實現系統低功耗的基礎。電源板主要提供CPU等數字電路+3.3 V/+1.8 V電源,地震計反饋電路供電±12 V、±4 V,參考電壓±2.5 V,標定電路和檢波器控制電路供電。GPS系統提供時間服務和地理位置信息。

AT91SAM9G20是Atmel公司推出的一款基于ARM926EJ-S核的低功耗SoC。ARM核工作頻率高達400 MHz,具有DSP指令擴展,支持Java硬件加速,具備全功能的MMU。內部集成2個容量為16 KB的高速SRAM,具有豐富的片上I/O設備,包括以太網MAC、USB主機和設備接口、通用同/異步發送接收器USART、SPI接口、同步串行接口SSC、多媒體存儲接口等。電源管理控制器(PMC)提供了CPU動態調頻的硬件支持。

1.1 FPGA邏輯設計

FPGA芯片的功能主要包括:(1)采集三個通道的A/D數據。當三路數據準備就緒,nDRDY1、nDRDY2、nDRDY3信號全部拉低,啟動由FPGA實現的SPI數據傳輸狀態機,地震波形數據被緩沖到FPGA內部的16 bit寬的FIFO_2k_ADC_DATA中。當FIFO_2k_ADC_DATA中數據達到一個閾值時,向ARM微處理器觸發AD_INT中斷。在中斷處理程序ad_irq_rx()中,通過系統數據總線把FIFO中數據轉移到內存緩沖區ad_data_buff[]中。之后,調用schedule_work(tasklet)把諸如數字信號濾波等耗時任務放到中斷下半部中進行處理。(2)根據標定數據文件,控制DAC生成模擬標定波形輸出。標定波形類型有正弦波、方波等。(3)檢波器控制電路驅動地震計調零電機動作。(4)IRIG讀碼。生成IRIG-B數據幀,通過PPS_interrupt觸發CPU中斷,pps_irq_handle()中斷處理程序負責把IRIG碼存儲到內存變量irig_frame中,等待解碼以提取時間、經緯度、高程等信息。下面是spi實體的Top-level行為級VHDL語言描述。

評論