基于FIFO的VXI總線并行A/D連續采集研究

1 引言

在工業領域的許多測試應用中,特別是產品研制的調試階段需要對一組信號進行長時間的連續采集記錄,以便在事后根據這組記錄的數據進行分析,或者檢驗研制產品的時序是否正確。一些VXI A/D采集模塊,存儲容量較小,如果連續循環采集,在一次采集和下一次采集之間會丟失數據,測試過程中不能實現實時監控信號,也不能夠實現連續采集數據。針對上述問題,本文在VXI總線并行A/D模塊上,結合FIFO,提出了一種可以實現大量數據長時間連續采集的方法。

2 VXI總線8通道并行A/D模塊設計

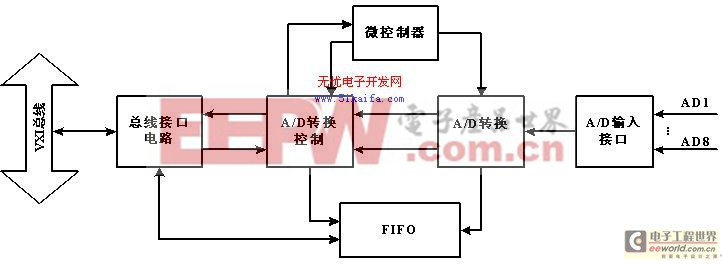

VXI總線8通道并行A/D模塊是A16的C尺寸寄存器基模塊。在A16寄存器基模塊中,其訪問空間限制在64字節內,而且每次訪問都必須對寄存器的狀態進行讀取判斷,很難滿足高速、大容量的數據傳輸要求。因此在A16空間里,實現高速、大容量的數據傳輸,是模塊設計的重點和難點。在該模塊的設計中,采用大容量FIFO芯片IDT7207作為內置緩沖器,采集數據先放在FIFO的RAM中。VXI總線可以將FIFO中數據以數據塊的形式進行高速讀取,可以解決高速、大容量的數據傳輸。電路框圖如圖1所示。

圖1 電路框圖

數據采集時,本地微控制器首先通過通訊寄存器接收VXI發送的狀態設置命令,如采樣頻率、采樣方式、采樣點數、程控增益,然后設置相應的寄存器后,啟動A/D,檢測A/D狀態,并將轉換值寫入FIFO。AD轉換結束,設置相應的寄存器,計算機通過判斷此寄存器的狀態,進行FIFO數據的讀取。

以上的設計中,采用大容量FIFO芯片IDT7207作為內置緩沖器,以數據塊的形式進行高速讀取,可以實現高速、大容量的數據傳輸。但是如果需要長時間的連續數據采集,IDT7207的容量(32K)仍然不能滿足要求。一個長時間的采集任務需要采用多次采集的方式,每次采集都需要發送啟動命令,然后等到A/D轉換結束,最后將A/D轉換數據塊讀入計算機。在兩次采集之間要讀轉換結束的數據,還需重新發送啟動命令,因此采集的數據是不連續的。

3 基于FIFO的連續采集實現原理

從上面的分析可以得出:要實現連續采集,就不能在兩次連續采集之間有間隔。因此一種方法是讓VXI模塊的A/D轉換和計算機的讀取A/D轉換數據并行進行。當計算機啟動AD轉換后,VXI模塊內的A/D控制器負責不停的往存儲器中寫入轉換后的A/D數據,計算機異步讀出存儲器數據。先進先出結構FIFO能滿足這種要求。IDT72××系列中的IDT7207是IDT公司生產的一種高速、低功耗CMOS型FIFO雙端口RAM, 它的存儲容量為32k×9bit.,存儲時間為12ns。該芯片內的雙端口RAM具有2套數據線,分別實現數據寫入和讀出功能,各自獨立的讀寫指針分別在讀、寫時鐘的控制下順序地從RAM中讀、寫數據。讀、寫指針通過RAM的最后一個單元加1回到第一個RAM單元的方式實現循環。比較和控制部分提供數據空標志(/EF)和數據滿標志(/FF)來防止存儲器滿時再寫入數據的溢出操作和存儲器空時的存儲器空讀操作。而半滿標志(/HF)可以用來防止數據丟失和提高數據傳送效率。其結構如下圖2所示。

圖2 FIFO芯片IDT7207結構圖

本文中要實現長時間的連續數據采集而不丟失數據需要利用FIFO的這個半滿標志。當啟動VXI模塊的A/D轉換后,計算機便監視FIFO的狀態,看是否半滿。如果不是半滿,不做操作;如果半滿便讀取FIFO中的一半數據。其過程見下圖3。

圖3 連續采集時FIFO的數據讀取

在模塊硬件電路的實現中,將FIFO的空標志、滿標志和半滿標志引入到VXI模塊的狀態寄存器中。從而可以通過讀地址為0X4的狀態寄存器的值來判斷FIFO的狀態。狀態寄存器的狀態字如下所示:

D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

其中D15為GND;D14為MODID*;D13為FIFO的滿標志,低有效;D12為FIFO的半滿標志,低有效;D11為FIFO的空標志,低有效;D9為VXI命令寫準備好標志,高有效;D8為VXI命令讀準備好標志,高有效;D3為READY;D2為PASSED;D0為DONE;D1,D4不確定。

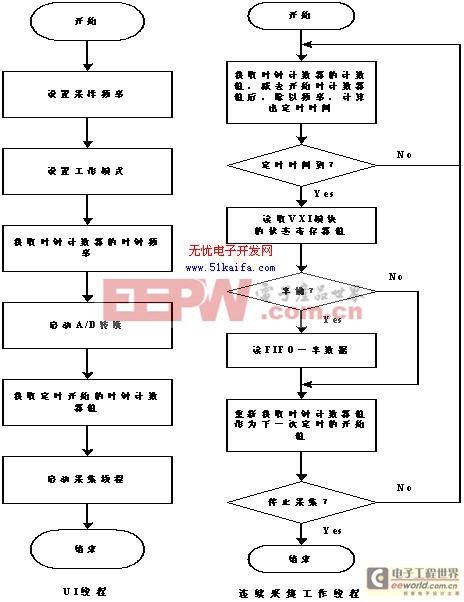

4 連續采集應用程序軟件設計

為了實現連續采集計算機的應用程序需要定時查詢VXI模塊的狀態寄存器。Windows操作系統中提高了兩種級別的定時器:一般級別的定時器和高精度定時器。Sleep()和GetTickCount()是屬于一般級別的定時器,它們利用系統的“Tick”時間作為計時單元,定時精度為10ms。而本文設計VXI A/D采集模塊的最高采樣率為200kHZ, A/D采集模塊中的FIFO容量為32k,如果以高采樣頻率100kHZ八通道方式進行采集,查詢定時間隔為10ms,采用Sleep()或者GetTickCount()定時時10ms誤差會使得每次定時內約有10/1000×100×1000×8=8k個點留在FIFO中。在采集過程中可能出現以下情形:第一個10ms定時,如果定時精確則轉換8k個點,由于誤差造成多轉換7999個點,總共轉換16k-1個點,FIFO還未半滿;然后再定時10ms,如果情形和第一次類似轉換16k-1個點,兩次轉換后FIFO中總共存在32k-2個點,此時開始讀一半FIFO數據,那么由于在讀數據中模塊還要進行A/D數據的轉換和存儲,會因為FIFO中數據未及時讀走造成FIFO滿而丟失數據。

Widows95以后的操作系統版本提供了QueryPerformanceCounter()函數和QueryPerformanceFrequency()函數,可以實現更高精度的定時,并要求計算機從硬件上支持高精確計時器。在進行定時之前,首先調用QueryPerformanceFrequency()函數獲得計算機內部時鐘計數器的時鐘頻率,然后在需要高精度定時的代碼兩端分別調用QueryPerformanceCounter()函數獲得時鐘計數器的計數值,利用兩次獲得的計數值之差及時鐘頻率,計算出定時的精確時間。其定時精度為計算機內部的時鐘頻率,可以達到微妙級。

因此在需要使用較高采樣率的場合中,須使用高精度定時。在實際的連續采集應用中,可以將連續采集放到專門的工作線程中,與UI線程序分開,避免UI線程以及其他線程的操作及消息傳遞影響連續采集工作線程。實現流程如下圖4。

圖4 實現流程

5 連續采集的應用

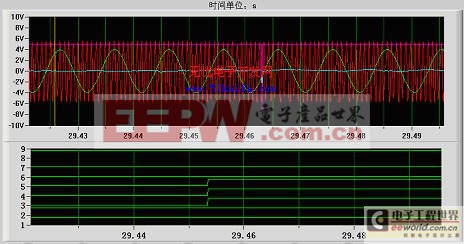

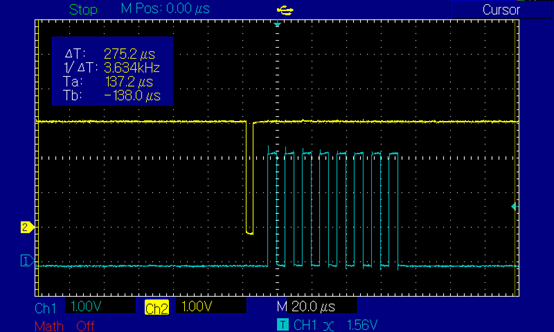

該方法已被應用于某裝備測控系統中,下圖5所示為采集完后,采集數據的回放情形。

圖5 采集數據回放

采樣數據放大后,如下圖6。

圖6數據放大

6 結束語

在很多的測試需求中,都需要長時間的連續A/D采集和記錄。因此本文研制了帶FIFO的VXI總線A/D模塊,給出了采用該模塊實現長時間大容量連續A/D的有效方法,此方法已經成功應用到某裝備測控系統中。本文創新點:1 研制帶FIFO的VXI總線A/D模塊。2 實現基于FIFO的VXI總線連續數據采集。

參考文獻:

[1] Integrated Device Technology Inc.IDT7207 Data Sheet.2001.5

[2] 張毅剛等.自動測試系統.哈爾濱:哈爾濱工業大學出版社,2001

[3] 龍姝穎等.一種基于CPLD的多通道數據采集系統的設計.微計算機信息,2006(07Z):203-204,136

[4] 李愛華 王章瑞.高速FIFO存儲芯片IDT7207在虛擬邏輯分析儀設計中的應用.儀表技術與傳感器,2003(3):39-42

評論