基于SOPC的觸控屏控制器IP核設計與實現

文中提出一種針對TFT-LCD觸控屏控制器IP核的設計方法。該控制器具有Avalon總線接口,與其他標準IP核一起構成以NiosⅡ為核心的片上系統。針對本設計中觸控屏幀緩存讀操作的特點,選擇以Avalon主端口接口的形式對模塊進行開發,大大提高了處理器運行效率,同時實現了觸控屏控制器IP核的參數化設計,提高了控制器對于不同LCD屏的可復用性,最后通過對輸出緩沖FIFO的使用,解決了數據讀出時鐘與像素時鐘不同步問題。

1 觸控屏控制器總體結構

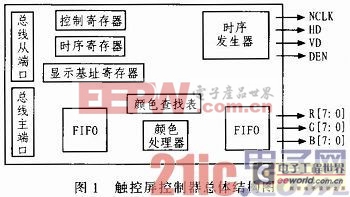

在SDRAM中開辟一段儲仔空間,用來存放屏幕圖像數據,稱之為幀緩存。通過設計適當的硬件邏輯來建立幀緩存與屏幕圖像像素之間的一一對應關系,并配合觸控屏顯示所必需的行、場時序信號,將幀緩存中的數據不斷地輸送給觸控屏,完成最終的顯示刷新,其總體結構如圖1所示。

觸控屏控制器刷新周期開始時,主端口模塊根據幀緩存地址生成邏輯所產生的地址,完成主端口的讀操作,實現幀緩存中數據讀取,并將該數據輸送給輸出緩沖模塊。同時,時序信號生成模塊依據觸控屏的時序規范生成行、場同步信號,以及與像素同步的相關顯示點的橫、縱坐標。觸控屏控制器數據顯示模塊不斷從緩存中讀取屏幕顯示數據。

2 觸控屏控制器模塊設計

2.1 Avalon-MM Slave接口模塊

本模塊掛載在Avalon總線上作為從設備使用,用來對所有的用戶邏輯進行配置和控制,核心功能是寄存器操作,包括讀、寫以及一些特殊指示與狀態信號的產生與轉換。通過從端口得到的數據分別賦值給相應的寄存器,寄存器分為:FIFO地址寄存器、坐標寄存器、一幀數據長度奇存器。本模塊是最后在觸控屏上實現圖形顯示功能的接口電路。

2.2 Avalon-MM Master接口模塊

LCD控制器的本功能是產生LCD時序信號,將幀緩存中的圖像信息進行有序輸出。由于圖形是一幀一幀地輸出到觸控屏上,而且顯示刷新過程是無限循環的,所以必須反復執行幀緩存讀操作,因此本設計對上述讀操作進行了硬件加速。可以不斷地從FIFO讀取圖像數據,并且在行、場和觸控屏顯示有效時間段讀取圖像數據,其它時間不讀圖像數據,這樣減少了Avalon總線的使用,有利于圖像顯示并減少了總線負擔分析讀幀緩存的操作可以發現,該過程總是按照一定的順序,將存儲器中的數據讀出來進行顯示輸出,規律性非常強。

本模塊主要完成地址及操作時序的產生、像素數據緩存寫操作控制、數據寬度的變換等功能。

2.3 觸控屏時序產生模塊

本文的觸控屏引出信號線有5根:像素數據信號、觸控屏時鐘信號、行同步信號、場同步信號、使能信號。為了實現觸控屏的正常顯示,必須對以上信號按照規范的時序進行驅動,其中,行、場同步信號分別用來標記屏幕上一行和一幀圖像的顯示時間,屏幕掃描線從上到下、從左到右依次掃描。在這個過程中,只需將幀緩存中的圖像像素數據依次輸出,就可以實現屏幕圖像顯示。

2.4 FIFO幀緩存模塊

DDR控制器隨著系統時鐘不斷往FIFO寫數據,當一幀數據寫滿時就不再進行寫狀態,而等待LCD控制器進行讀狀態,顏色處理器從FIFO中獲取數據,每次從FIFO中讀取32 bit數據并不斷送給LCD。

顏色處理器將每一個字節作為一個像素數據,并將一個字節的像素數據轉換為3個字節的RGB數據。顏色處理器從同步FIFO緩沖器中讀取數據,當同步FIFO緩沖器寫和讀相互不沖突時,同步FIFO緩沖器產生讀請求,讓Avalon主端口向Avalon總線發起讀傳輸,從總線上獲取的數據將寫入同步FIFO緩沖器,顏色處理器從FIFO中讀取像素值,并且傳給LCD顯示模塊。

評論