基于CS5321與CS5322多路數據采集

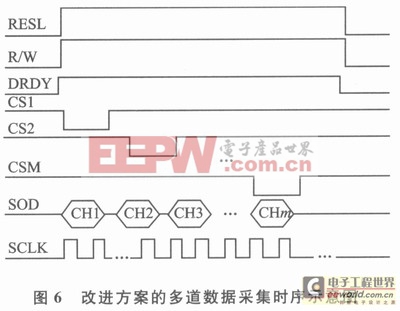

CS5322 的 DRDY為數據準備好信號引腳。當DRDY為高電平時,表示CS5321/CS5322組成的∑一△A/D轉換器已經進行完一次轉換,并已由CS5322將數據在其輸出緩沖器中準備好,數據可以從串行口輸出。CS5322中讀操作控制插針有CS、R/W、SCLK、SOD。當CS=O且R/W=1時,串行口處于讀操作有效。RSEL引腳用來選擇串口輸出的是數據緩沖器,還是狀態緩沖器的數據,SOD為串行數據輸出插針。當讀狀態被選擇后,不管SCLK是高電平還是低電平,第一位輸出數據都會在SOD插針出現,并且在SCLK的下降沿終止。第一個SCLK下降沿后,每一個SCLK的上升沿從SOD引腳輸出一位數據。輸出的位流順序為高位(MSB)在前低位(LSB)在后。

2.2 多通道串行接口的原理

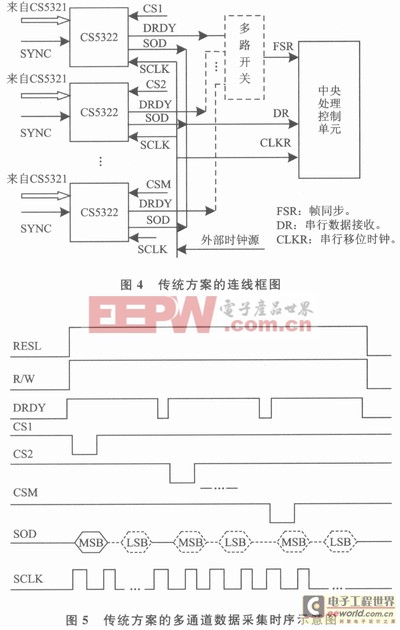

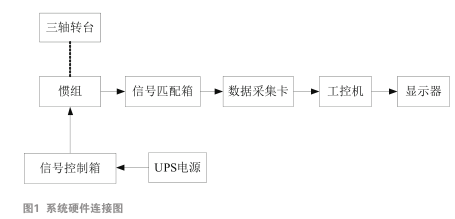

通過以上對CS5322的串行讀操作時序的分析,可以得到利用CS5321/CS5322實現的多通道數據采集系統的傳統方案。以M通道為例,系統的框圖如圖4所示。

在由CS5321/CS5322組成的∑一△A/D轉換器的多通道采集系統中,傳統方案如圖4所示。通過控制器輪流接通各道的DRDY信號,在DRDY為高電平時各道輪流從SOD引腳將數據輸出到控制器。由CS5321/CS5322所組成的∑一△A/D轉換器的采樣率,由DECC、DECB、DECA三位設定,可以為62.5 Hz~4 kHz等7種。對應每一種采樣率,所要求的移位時鐘(SCLK)的最低頻率fmin=fs×24(fs為采樣率)。在典型用法中,只需要根據采樣率要求設計一個時鐘源,使它的頻率略高于,fmin即可。時序示意如圖5所示。

2.3 對傳統方案的改進

按照上述方案,雖然可以完成多通道數據采集系統的設計,但是用這種方案設計的多通道數據采集系統完成一次多道數據采集傳送的周期(T=m×24/fs)很長,特別是圖5 傳統方案的多通道數據采集時序示意圖隨著m的增大,即通道數的增加,T將成倍增加。

通過對CS5321/CS5322的進一步研究發現,CS5322對SCLK要求的最小周期可以為100 ns,遠遠高于傳統的設計方法所采用的移位時鐘頻率。因此,可以通過加快串行移位時鐘(SCLK)來加快讀出數據的速率,從而實現在一個采樣周期內讀出多道的數據。

假設SCLK的頻率為fb,則每道的24位的數據需要的移位時間為tm=24/fb,又采樣周期為Ts=1/fs(fs可以為62.5 Hz、125 Hz、250 Hz、500 Hz,1 kHz、2 kHz、4 kHz),fb的最大值可以達到10 MHz,只要適當提高fb就可以使tm《Ts,這樣在一個采樣周期里最多可以完成Ts/tm道數據傳送,大大地提高了多通道數據采集傳送的速度。例如,當fs=1 kHz,fb=1 MHz,則由以上分析可知, 理論上一個采樣周期里最多可以傳送42個通道的串行數據。考慮到器件延時等多種因素,實際應用中應比此理論值小。

改進后的連線框圖,是在圖4的基礎上去掉虛線部分,直接將第一通道的DRDY與FSR相連即可。改進方圖6 改進方案的多道數據采集時序示意圖改進后的多路∑一△A/D轉換器同時進行卷積運算和數據轉換,并幾乎同時產生DRDY信號,但只有第一道的DRDY信號接到控制器的幀同步引腳(FSR),來觸發處理器的串口接收1幀數據。各通道的片選CSl、CS2……CSm由控制器在一個采樣周期里依次選中,各通道的SOD引腳都直接連接到控制器的DR引腳,整個系統的移位時鐘可以由外部時鐘源提供,也可以由控制器產生。

整個系統的數據采集過程如下:①初始化,啟動A/D。②將A/D轉換器的R/W置高電平,并設置采樣率。③當DRDY變為高電平,同時使CSl有效,開始第一道數據采集;當24位數據全部接收完畢,第一道完成,使CS2有效,開始第二道采集,依次完成M道數據采集。④將數據存儲并處理。

結 語

目前,基于CS5321與CS5322的多路數據采集系統在石油勘探、地震數據采集領域已經得到應用。與其他具有相應用途的數據采集系統相比,本系統的采集速率更快,精度更高,實時性更好。本文介紹的多通道數據采集系統的設計思想有一定的通用性,并且對傳統方案作了一些改進,可以進一步提高整個系統的采集速率。

評論