用于高速ADC的低抖動時鐘穩定電路的設計

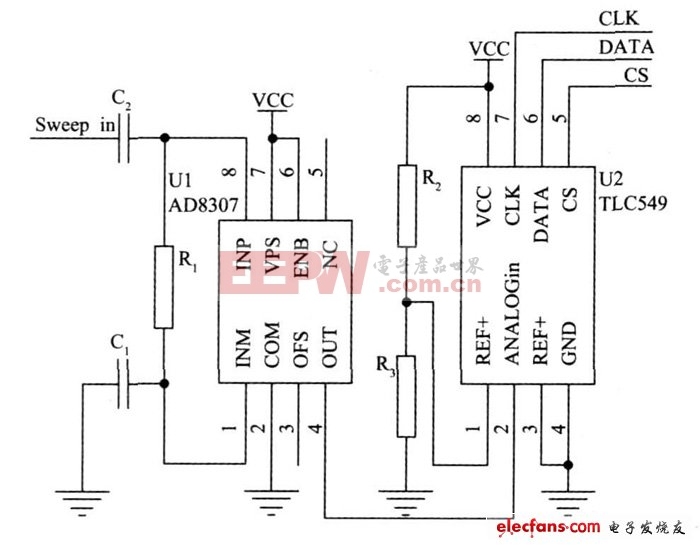

由m0、ml、m2、m3組成的鏡像是運算放大器的啟動電路,在運算放大器不工作時對電容C1充電。電阻R1和電容C1構成一個RC濾波器,對信號起到濾波的作用。m4、m5、m6三個晶體管構成DLL的延遲線(VCDL)。在這個電路中只需要一級延遲就足夠了。在這個延遲線旁邊的電容C2的值越大,則延遲越多。C2旁邊三個反相器構成一個鎖存結構,它的主要作用就是輸出一個比較理想的方波。

2. 2電路仿真與分析

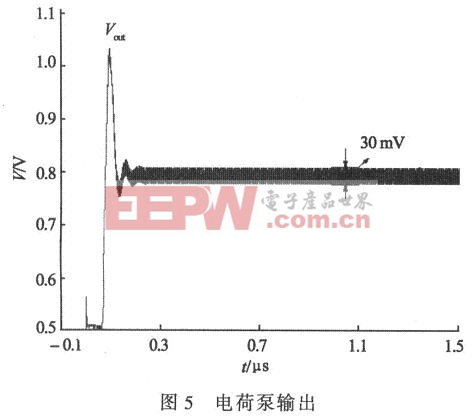

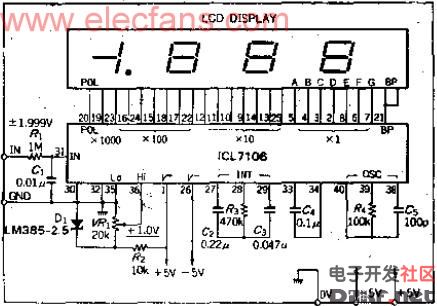

對圖4的電路,在Cadence spectre環境下進行了仿真。輸入電平的周期為4 ns,時鐘占空比為45%,基準電壓為3.3 V。運算放大器與電容c.組成電荷泵。電荷泵的輸出見圖5。時鐘穩定電路穩定工作,Vout有30 mV的波動,Vout波動越小表示壓控延遲線時鐘輸出的抖動越小。

此外,還可以得到,運算放大器的閉環增益為75.074 9 dB。0 dB對應的相位為一109.818°,所以它的相位裕度為70.182°。顯然,該運算放大器的參數是比較好的。

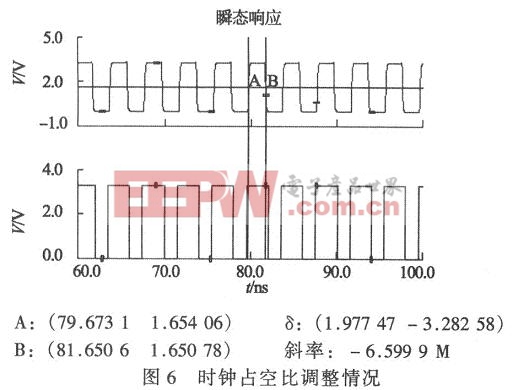

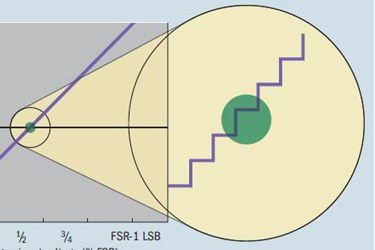

圖6為時鐘占空比調整情況。從圖中可以看出該DLL能調整占空比到49.4%(1.977 4/4≈49.5%)。實際上該時鐘穩定電路在時鐘周期4 ns時,能調節25%~75%的占空比接近于50%左右;而在時鐘周期10 ns時,可調節的范圍達到10%~90%。

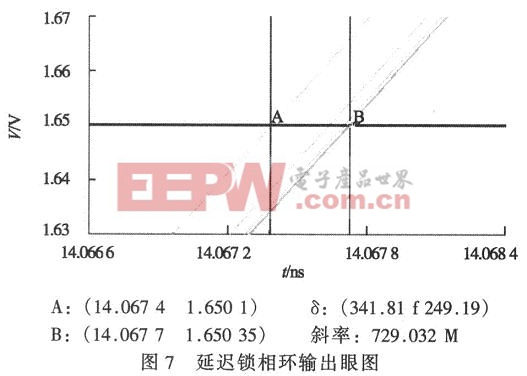

圖7為延遲鎖相環的輸出眼圖。其實在A、B之間有幾百條上升沿。從圖中可以看出,峰.峰值抖動為341.8l fs。對于250 M這個抖動值已經相當小了。

3 版圖設計

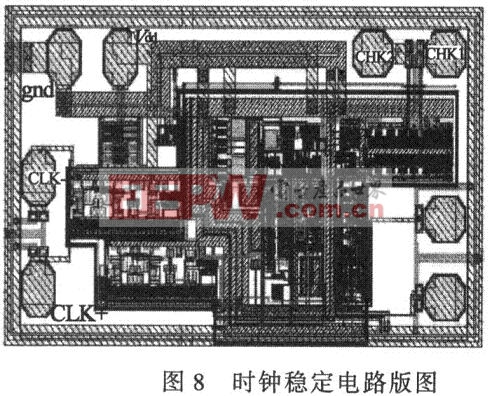

利用JAZZ提供的PDK進行工藝接口,版圖設計由該公司提供相應規則,具體針對線寬、接觸孔、通孔、線距等作了相關規定,并且設計過程中充分利用該公司提供的Pcell作相應的版圖設計,這樣相應工作得到了很多的簡化。具體的設計規則涉及IP問題,故略去。本文給出時鐘穩定電路的整個版圖,如圖8所示。

該芯片總面積為0.74 mm×1.44 mm。其中,最左邊的CLK一,CLK+為輸入端,本文只用到CLK一一端作為輸入端就足夠了;右上角的CHKl、CHK2為輸出的大管子;最中間為運算放大器。

4 結語

本文介紹了用一個簡單的延遲鎖相環來實現高速A/D轉換器中的時鐘穩定電路。該延遲鎖相環具有兩個作用:(1)調節采樣時鐘占空比;(2)控制采樣時鐘的抖動。本文以一些典型的基奉模擬IC為設計基礎,著重對延遲鎖相環電路的各個單元電路設計逐一進行了分析和研究,并對總體電路進行了功能和參數的模擬分析,其結果較為滿意。在此基礎上進行了工藝及版圖設計和分析,在完成工藝版圖設計后,采用DRC、ERC、Calibre、Extract和LVS等CAD工具對版圖進行了參數提取及驗證工作,保證了電路和版圖的一致性。

評論