基于門控時鐘的低功耗電路設計方案

集成電路工藝節點的提升帶來了芯片集成度的極大提高,同時也導致了功耗的急速增加。另外,市場對電子設備的大量需求使得系統功耗成為系統性能的一個重要指標,功耗的高低成了芯片廠商競爭力的焦點之一,功耗控制與管理已成為絕大多數芯片廠商首要考慮的問題。SoC設計的功耗包含兩部分:靜態功耗和動態功耗。靜態功耗主要由泄漏電流引起,在130 nm工藝下,靜態功耗相對較小,可以忽略不計。動態功耗主要包括短路功耗和翻轉功耗,是本設計功耗的主要組成部分。短路功耗即內部功耗,指由器件內部由于P管和N管在某一瞬間同時導通引起的瞬時短路引起。翻轉功耗由CMOS器件的輸出端負載電容充放電引起。芯片工作時,很大一部分功耗是由于時鐘網絡的翻轉消耗的,如果時鐘網絡較大,這部分引起的功耗損失會很大。在眾多低功耗技術中,門控時鐘對翻轉功耗和內部功耗的抑制作用最強。本文主要講述門控時鐘技術的具體實現。另外,基于高閾值單元具有較低的功耗,設計采用高閾值單元庫。

1 門控時鐘技術的基本原理

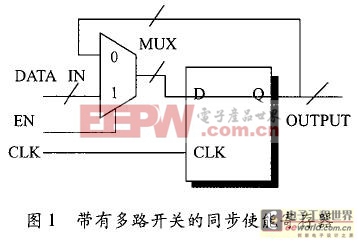

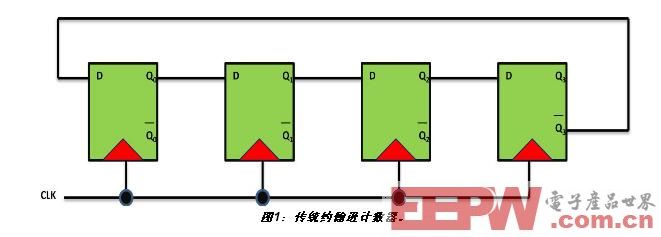

對于一個設計中的寄存器組,經DC編譯后一般會生成如圖1所示的電路。由圖1可以看出,當EN為1時, DATA_ IN的值由多路開關傳至寄存器組的數據輸入端,當CLK上升沿來臨時,傳至DATA_OUT。當EN為0時, OUTPUT保持不變。但由于時鐘信號CLK的翻轉,寄存器組會持續在CLK的上升沿來臨時讀取數據輸入端的數據,而這時讀取的數據是不變的,這就消耗了額外的功耗。

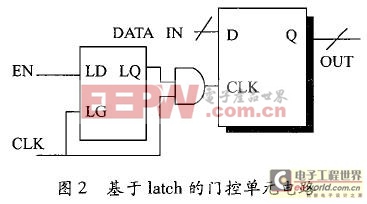

為保證此時寄存器組不受時鐘翻轉的影響,可在EN信號為0時關斷寄存器組的時鐘輸入端,使其不受CLK端的變化而變化,這一操作可通過門控時鐘技術來實現,如圖2所示。圖中的門控單元由一個Latch和一個與門組成。門控單元也可以采用非latch結構,直接由與門或或門組成。但由于這種電路會引發毛刺,故此處采用基于Latch的門控單元電路。插入門控時鐘后,當EN為1時, Latch單元在時鐘低電平時將EN鎖存至ENL,時鐘上升沿來臨時, ENCLK隨CLK變化,寄存器組執行正常的讀入讀出操作。當EN為0時,寄存器時鐘輸入端ENCL保持為0,不隨源時鐘CLK的翻轉而變化,故此時寄存器組不消耗額外功率。

由此可見,插入門控時鐘能消除寄存器組冗余翻轉引發的內部功耗,同時由于多路選擇器組被一個基于latch的門控單元代替,所以也減小了電路的面積。

另外,為了進一步減小設計的功耗,可采用一些特定的門控技術。目前應用比較廣泛的有多級門控時鐘,層次化門控時鐘等。在多級門控時鐘技術中,一個門控單元還可用來驅動其他一個或一組門控單元。這樣就通過分級控制減少了門控單元的數目,而且這種方法可組合盡可能多的寄存器組使得門控單元向頂層靠近,節省更多功耗。

2 門控時鐘的物理實現

電路在功能仿真通過后,開始進行寄存器級綜合。采用高閾值標準單元庫和多級門控時鐘技術相結合,在RTL階段插入門控時鐘單元,并在布局布線時在IC Compiler中進行了基于門控時鐘的布局布線優化,布局布線正確完成仿真通過后,在PT中做靜態時序分析并進行最終的功耗分析。以下分三個部分講述。

2. 1 時鐘門控的RTL級實現

在RTL級,門控時鐘的實現不需要對設計本身進行修改,而只需在綜合腳本中加入一些控制項。

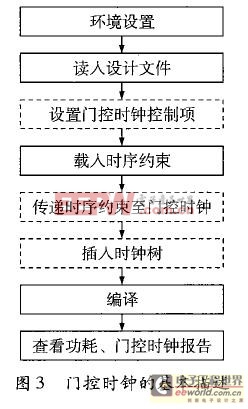

本文采用多級門控時鐘,相關的腳本如圖3 所示。

圖中,傳統的綜合流程用實線標出。虛線部分為門控時鐘的操作。

控制項set_clock_gating_ STyle是門控時鐘的核心。它的參數大小決定門控時鐘的質量,對功耗的優化效果和對CTS的影響。目前尚無完備的體系介紹如何設置控制項以使門控效果達到最優。本設計中有以下各個參數的設置方法。

首先確定時序單元的類型。為了避免非Latch單元易產生毛刺的缺點,此處選定時序單元的類型為Latch。由于庫中提供基于鎖存器的門控單元,固正邊沿邏輯positive_edge_ logic采用工藝庫提供的專用單元。采用集成單元的優勢在于不僅不需要設置門控單元輸入端建立時間和保持時間,因為集成單元的時序信息在單元庫中已有說明,而且有效緩解了插入門控單元對延時帶來的不利影響。以下重點闡述實驗中bi

評論