上電時實現延時系統復位的IC

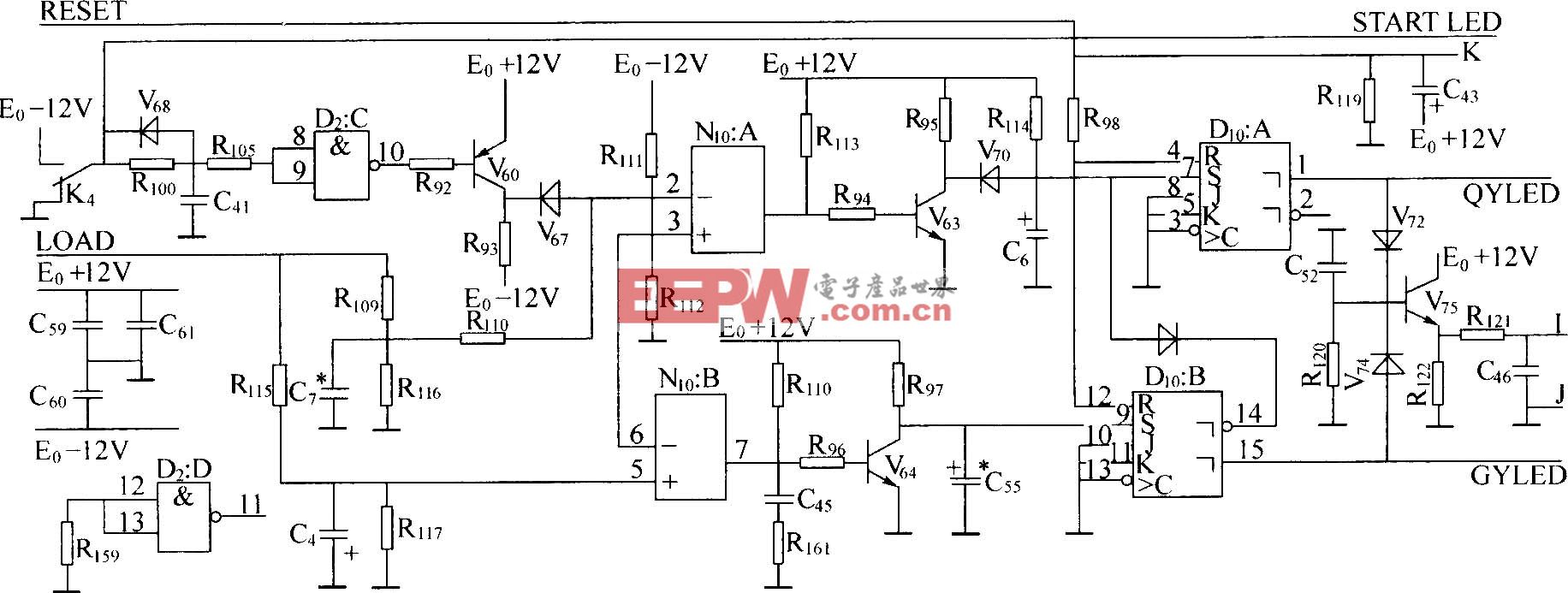

通過給晶體管增加一些電容、二極管和電阻,使用保持時間可調的復位IC,將純手動復位轉換為自動復位。

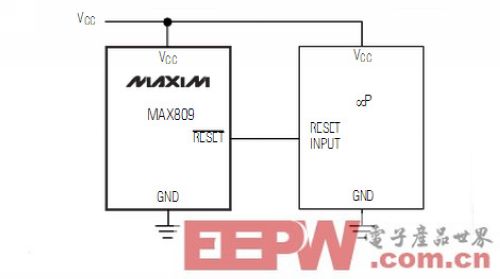

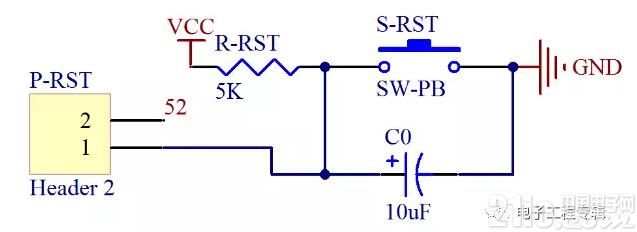

在大多數應用中, (手動復位)引腳通常與開關相連,為管理芯片制造手動復位信號。隨后,在預先設定的有效延時時間后,其從低電平有效復位回到高電平狀態。手動復位適用于大多數應用;然而,它需要人為干涉產生復位信號。在一些應用中,手動復位存在爭議,因為系統每次上電時都要執行。

(手動復位)引腳通常與開關相連,為管理芯片制造手動復位信號。隨后,在預先設定的有效延時時間后,其從低電平有效復位回到高電平狀態。手動復位適用于大多數應用;然而,它需要人為干涉產生復位信號。在一些應用中,手動復位存在爭議,因為系統每次上電時都要執行。

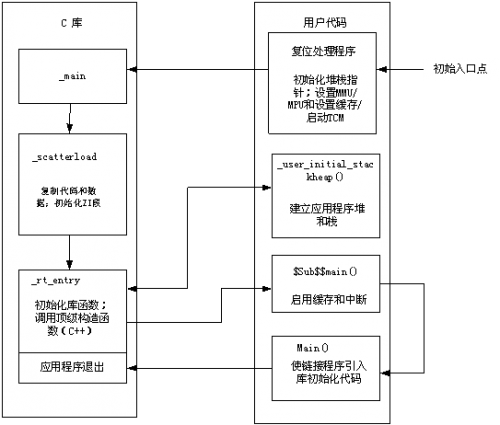

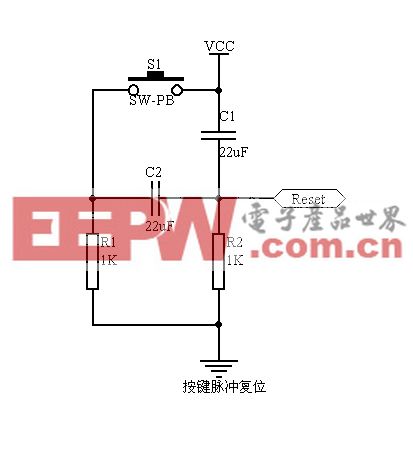

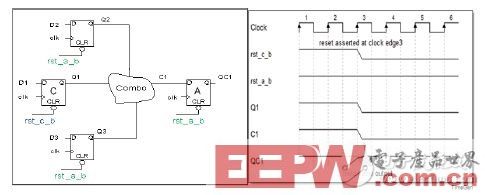

更進一步,包括嵌入式處理器在內的應用需要復位輸出為保持高電平——也就是說,非有效——在應用復位或低有效之前的某個時期。如圖1電路在設備上電時無需按下復位鍵的情況下,被證實是有效的,因為在復位的低信號到來之前,復位自動以預先設定的保持時間發生。

電路使用帶 引腳和低有效輸出

引腳和低有效輸出 的復位管理芯片。通常

的復位管理芯片。通常 輸入的內部上拉電阻為20到50kΩ。上電期間,

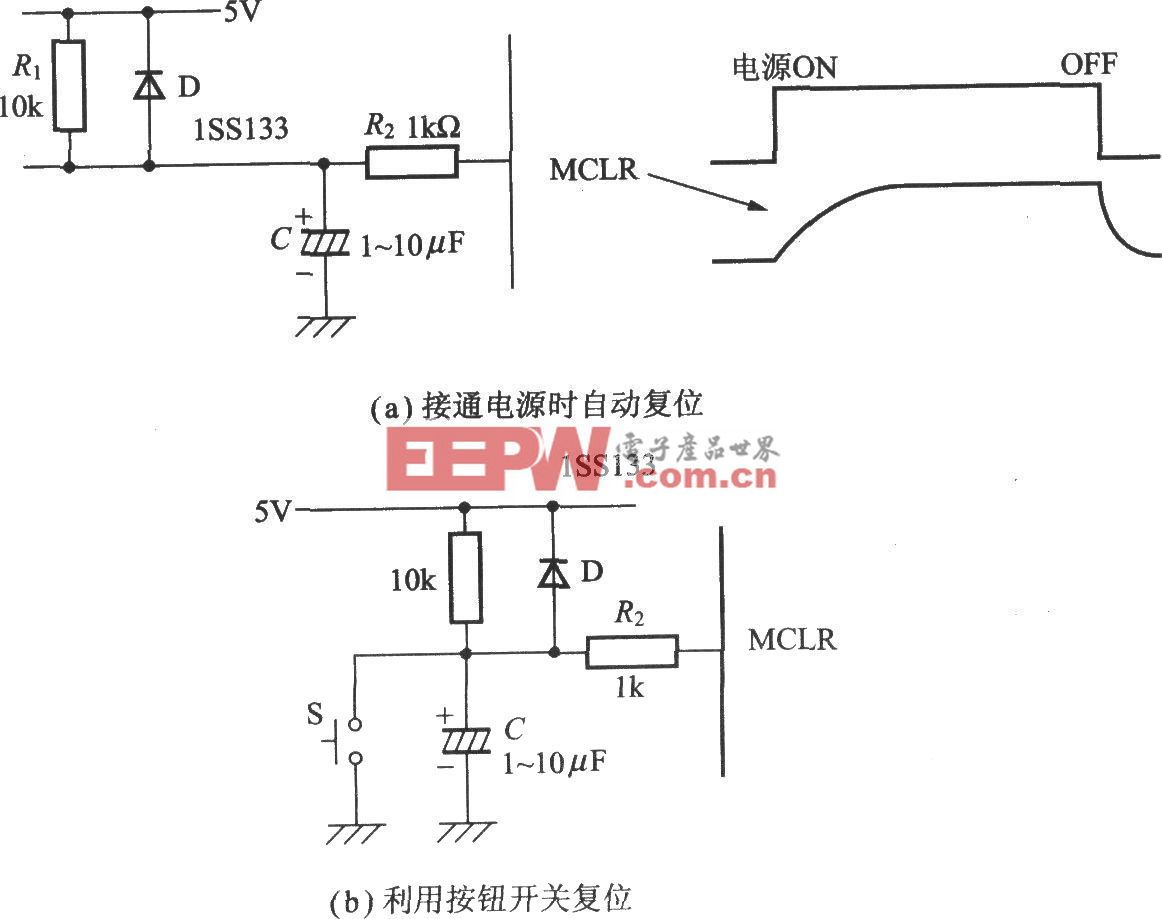

輸入的內部上拉電阻為20到50kΩ。上電期間, 內部電阻將電容C1充電到正向最大值VDD。為管理芯片產生

內部電阻將電容C1充電到正向最大值VDD。為管理芯片產生 復位輸入,其

復位輸入,其 輸入必須接收低有效的地信號,需要晶體管Q1導通。這個導通的時間長度取決于R1和C2的RC時間常數。這兩個器件決定Q1什么時候導通,從而為

輸入必須接收低有效的地信號,需要晶體管Q1導通。這個導通的時間長度取決于R1和C2的RC時間常數。這兩個器件決定Q1什么時候導通,從而為 輸出提供保持時間可調的高電平。為增加保持時間,增加R1和C2的RC時

輸出提供保持時間可調的高電平。為增加保持時間,增加R1和C2的RC時

間常數即可。

復位管理芯片只在 管腳的電壓超過觸發閾值電壓和管理器內部復位周期結束時,產生

管腳的電壓超過觸發閾值電壓和管理器內部復位周期結束時,產生 輸出。這個延時時間濾除了所有輸入電壓的毛刺。因為Q1的導通,使C1的負向變為地。而C1的正向不能立即改變極性,其被拉低并通過

輸出。這個延時時間濾除了所有輸入電壓的毛刺。因為Q1的導通,使C1的負向變為地。而C1的正向不能立即改變極性,其被拉低并通過 輸入的內部上拉電阻,緩慢的再次充電。當達到復位芯片的閾值電壓時,一旦達到芯片的延時時間便輸出復位信號。C1的選擇并不嚴格。然而,它的值應該盡量大——例如0.1到10μF——使C1和內部上拉電阻所得的RC時間常數足夠大。這個值確保C1在

輸入的內部上拉電阻,緩慢的再次充電。當達到復位芯片的閾值電壓時,一旦達到芯片的延時時間便輸出復位信號。C1的選擇并不嚴格。然而,它的值應該盡量大——例如0.1到10μF——使C1和內部上拉電阻所得的RC時間常數足夠大。這個值確保C1在 引腳上保持了至少1us的低電平。

引腳上保持了至少1us的低電平。

C2充電到Q1的偏置電壓后,晶體管仍然導通。在下一次上電或手動按鍵復位電路時,晶體管C2放電。這個動作一旦發生,Q1關閉。R1將C1的負向充電到供電電壓VDD。因為電容C1的正向不能立即改變,其表現為充電到2VDD。然而,保護二極管D1將C1的電壓箝位到僅為VDD加上二極管的導通電壓。一旦C2充電足夠使Q1再次導通時,重復循環。

pa相關文章:pa是什么

晶體管相關文章:晶體管工作原理

晶體管相關文章:晶體管原理 上拉電阻相關文章:上拉電阻原理

評論