Thunderbolt超高速I/O傳輸接口的ESD防護方案

Thunderbolt技術以1顆橋接PCIe以及視訊整合的晶片,能夠在3公尺的線長內傳輸達10Gbps的資料以及10瓦的供電,來作為界面控制,而接口在目前是先以銅纜來實現。在Intel與Apple的密切合作下,迅速地實際應用在Mac系列的產品上,以提供快速的資料傳輸服務。目前在Mac系列上的Thunderbolt是建構在mini-DisplayPort的實體接口上,其每條訊號線的傳輸速度規格如表1所示。而由于Thunderbolt是超高速的傳輸接口,在系統上屬于外露給使用者可以插拔的接口,必然是靜電放電(ESD)破壞的高風險區,因此ESD防護方案在此是絕對必要的。

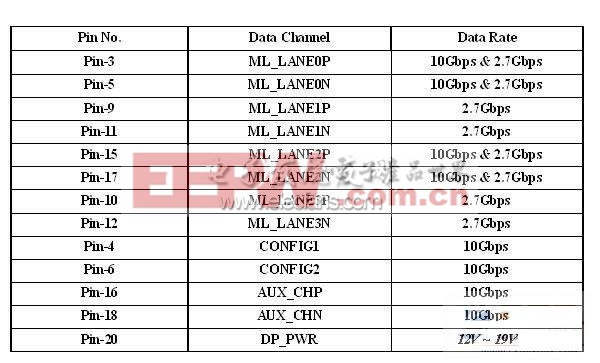

表1,訊號線傳輸速度規格表。

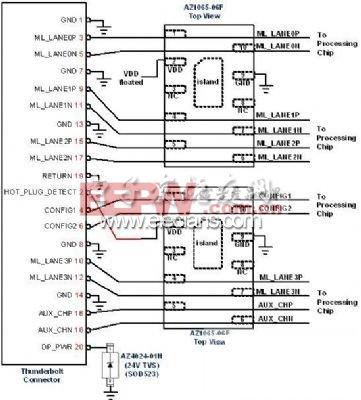

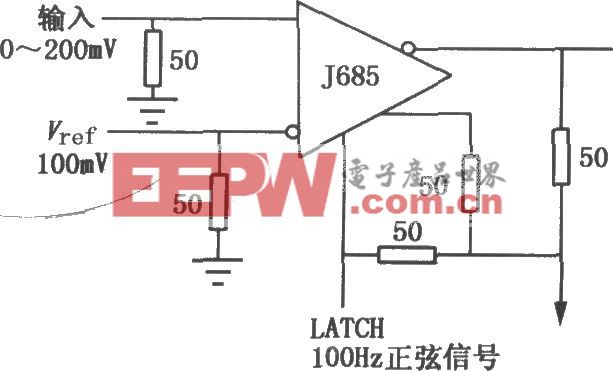

圖1,Thunderbolt完整的接口接線圖。

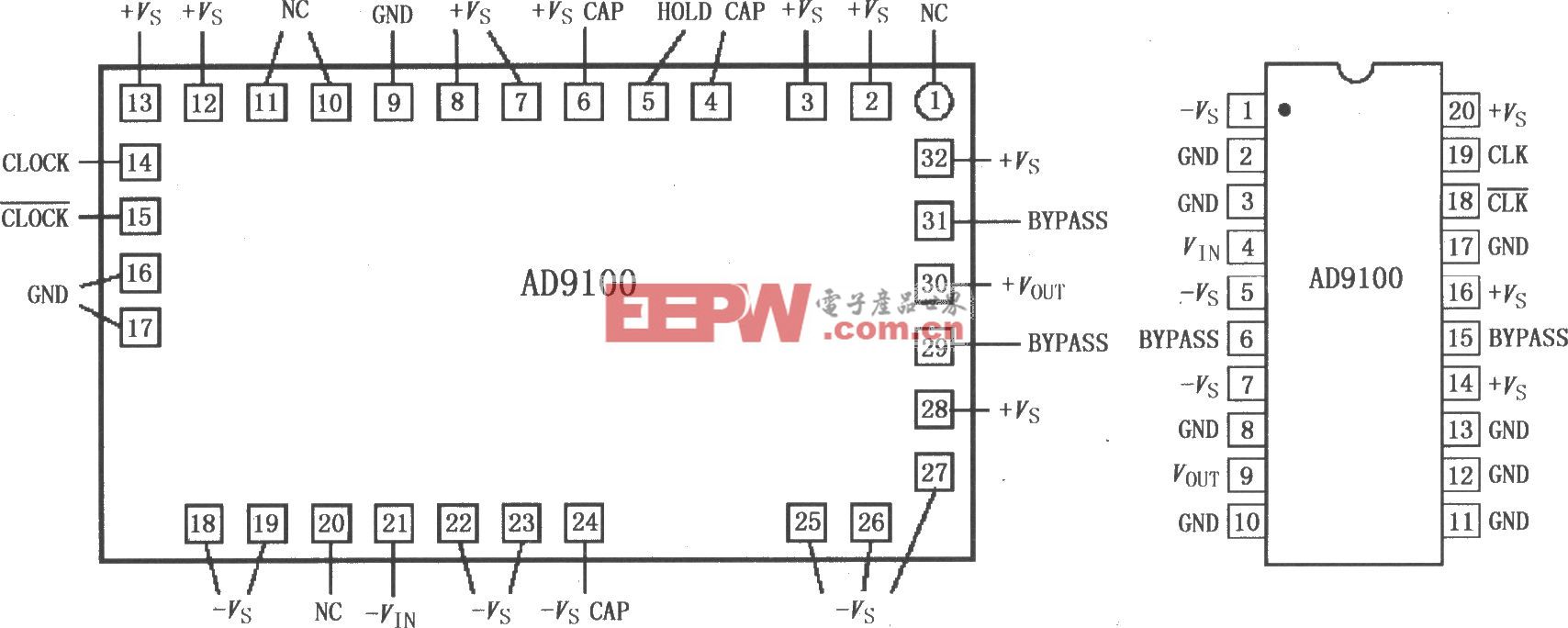

在設計Thunderbolt接口的ESD防護方案時,因為這個界面同時具備有數位影像以及數據傳輸的能力,因此在額外加入的ESD防護元件設計時,必須特別注意不可以影響到其超高速訊號的傳輸品質,為此晶焱科技特別設計了1顆ESD防護IC:AZ1065-06F,其每1根I/O接腳的寄生電容僅有0.27pF,可避免影響到高達10Gbps的訊號傳輸品質,而1個Thunderbolt接口僅需要2顆AZ1065-06F再加1顆AZ4024-01H就可以完整地保護此接口不受ESD的威脅,圖1即為完整的接口接線圖。

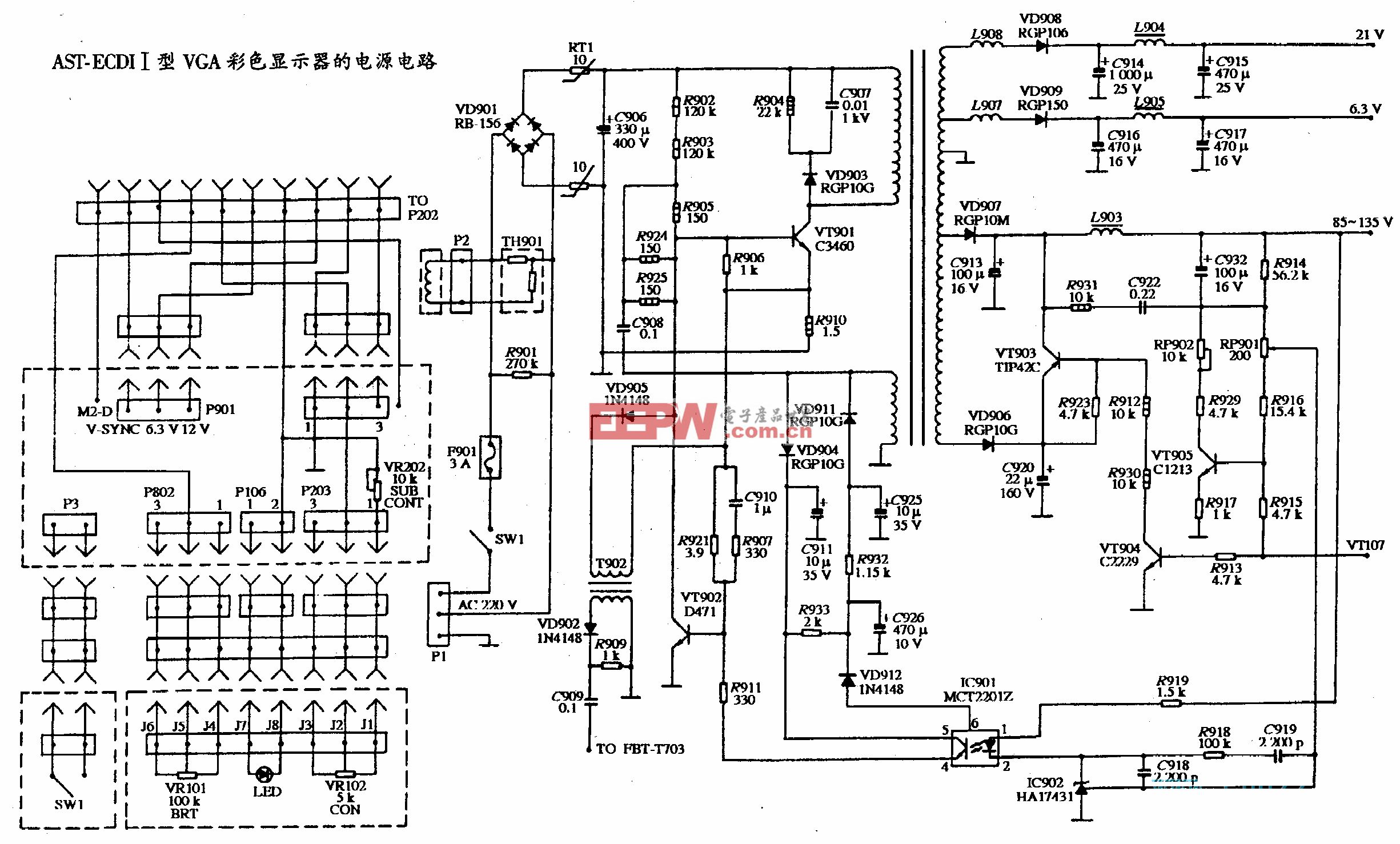

因為Thunderbolt接口的傳輸速率高達10Gbps,在設計ESD防護方案時,除了要盡量降低ESD防護元件接腳的寄生電容外,還必須維持PCB繞線(traces)的差動阻抗(differential impedance)不受影響,所以AZ1065-06F在設計時,還必須特別將其package接腳的空間間隔做特別設計,以符合維持PCB traces的differential impedance不會因為加上了AZ1065-06F而有所改變,圖2即為AZ1065-06F實際的PCB布局(layout)范例。

在ESD防護IC的接腳之寄生電容與空間間隔,符合了不影響訊號傳輸品質的要求后,接著就要檢視ESD防護IC所能提供的ESD防護效果。AZ1065-06F的每1根接腳對地,都被設計成可以承受IEC61000-4-2 contact mode 8KV以上的ESD轟擊,且其所提供的箝制電壓(Clamping Voltage)在6KV時僅有13V而已。因此AZ1065-06F除了本身的ESD防護性能力外,更結合了如圖1和圖2的接線與PCB layout設計,使得Thunderbolt接口可以承受高達8KV的ESD轟擊,而不會有受到破壞的危險狀況發生。這樣的設計可以大大地降低Thunderbolt接口因ESD轟擊而失效的機率,也是現今高速電子產品迫切需要的防護設計,因為這類高速接口對應的主要傳輸晶片,都是采用最先進的半導體制程所設計,這類先進制程的高速晶片本身對ESD耐受能力極為薄弱,所以非常仰賴接口的ESD防護方案。

評論