基于SoPC的實時視頻處理與顯示設計

當前基于軟核處理器的圖像系統已成為研究的熱點,使用FPGA來構建基于片上可編程系統(SoPC)的圖像處理系統,已成為一種趨勢[1]。因此,本文采用SoPC技術,在Altera公司單片Cyclone系列FPGA上使用IP資源復用技術集成了NiosII軟核處理器及各種輸入輸出接口,完成了對視頻圖像的采集、預處理、存儲和顯示幾大功能。本系統對圖像進行了灰度均衡化處理,使系統應用更廣。由于直方圖均衡能直接從已知的圖像中提取信息,不需要額外的參數說明,所以在軍用、航空、商業等領域,特別是紅外圖像增強領域[2]有實際的意義。SoPC是Altera公司提出來的一種靈活、高效的柔性設計,不需要修改硬件[3],就可方便地擴展和修改嵌入式視頻采集功能。同時,由于融入眾多的IP核,保證了設計的高效、快速。

1 系統總體結構及工作原理

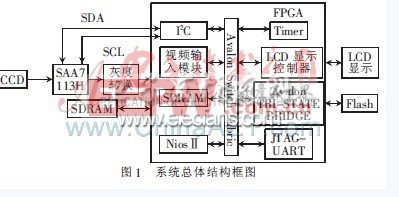

系統框圖如圖1所示。系統上電后,Nios II軟核中的I2C控制總線對視頻采集模塊SAA7113H進行配置,FPGA依靠像素時鐘和行、場信號同步采集SAA7113H芯片輸出的視頻信號中的灰度視頻數據,把采集到的灰度數據進行灰度直方圖統計和灰度分布均衡化處理。Nios II軟核外部加一個延遲模塊,與灰度轉換模塊輸出的信號同步之后,視頻輸入模塊開始工作,通過存儲控制、DMA控制器傳輸視頻信號,LCD顯示控制等模塊顯示所采集的信號。所有處理都采用流水線操作,大大節省了系統的處理時間。

2 系統硬件設計

2.1 視頻解碼芯片SAA7113H初始化

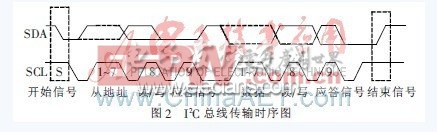

本系統中視頻解碼器的初始化配置由Nios II軟核處理器通過I2C總線完成,主要包括對視頻解碼器的工作模式,輸出行、場同步參考信號的時序關系以及輸出數字信號的格式等進行設置。I2C總線是由Philips公司開發的一種兩線制總線,由一條串行數據線SDA和一條串行時鐘線SCL組成,可以實現數據通信,完成芯片配置。首先,I2C總線控制器發出一個數據傳輸的起始條件:SCL信號保持高電平、而SDA信號由高電平變為低電平時,開始傳輸地址數據流。起始條件滿足后,發出一個8 bit的設備從地址,所有的外圍設備開始響應起始條件并轉換下一個8 bit寄存器地址(7 bit地址+1 bit讀寫位),由高位到低位依次傳輸。外圍設備識別出傳輸地址后,在第9個時鐘脈沖(確認位)把數據線變為低電平,然后開始將8 bit數據寫入或者讀出寄存器(讀寫位決定了數據的傳輸方向)。當時鐘線SCLK為高電平、而數據線SDA由低電平變為高電平時,表示一次數據傳輸完成,停止I2C總線,等待下一次的傳輸開始。圖2為I2C總線的數據傳輸時序圖。

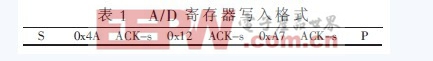

從SAA7113H的4個模擬輸入端AI11、AI12、AI21、AI22輸入的視頻圖像信號,經A/D轉換后產生數字色度信號和亮度信號,分別進行亮度信號處理和色度信號處理。亮度信號處理的結果送到色度信號處理器,進行綜合處理,產生YUV信號,經格式轉化后從VPO(8位)輸出。所有這些功能均是在I2C總線控制下完成。SAA7113的寄存器配置通過I2C總線來進行,遵從I2C總線協議。表1是SAA7113H寄存器的“寫”操作格式。

其中,S為起始位,條件是SCL為高電平、SDA有下降沿、ACK-s為從動設備應答位,P為終止位。在初始化過程中要注意:SAA7113H的節點地址(Slave Address)上電、RTS0為高電平時,其I2C寫地址為48H,讀地址為49H;RTS0為低電平時,其I2C寫地址為4AH,讀地址為4BH。

評論