襯底驅動軌至軌運算放大器設計

隨著便攜式電子產品和超深亞微米集成電路技術的不斷發展,低電源電壓低功耗設計已成為現代CMOS運算放大器的發展趨勢。降低功耗最直接有效的方法是降低電源電壓。然而電源電壓的降低,使得運算放大器的共模輸入范圍及輸出動態范圍隨之也降低。同時,電路電源電壓的降低將受到MOSFET閾值電壓的限制。針對這一問題,襯底驅動軌至軌技術應運而生,不但有效地降低了MOSFET的閾值電壓,從而直接降低了電路的電源電壓,并且使共模輸入范圍能夠達到全擺幅。但是襯底驅動MOSFET的輸入跨導小,輸入電容較大,從而限制了電路的最高工作頻率。因此,襯底驅動輸入級的引入,將不可避免地降低運放的第一級增益。為此,本文采用改進型前饋式AB類輸出級以增加有效輸入級跨導,從而避免了襯底驅動技術的缺點,使電路具有低壓低功耗高增益的特點。

本文設計的電路,采用襯底驅動技術,將電源電壓降至0.8 V,同時電路結合了恒定跨導控制電路和改進型前饋式AB類輸出級,能有效提高動態范圍和響應速度,使電路輸入級和輸出級均達到軌至軌,非常適合低壓低功耗模擬集成電路應用。

1 電路實現

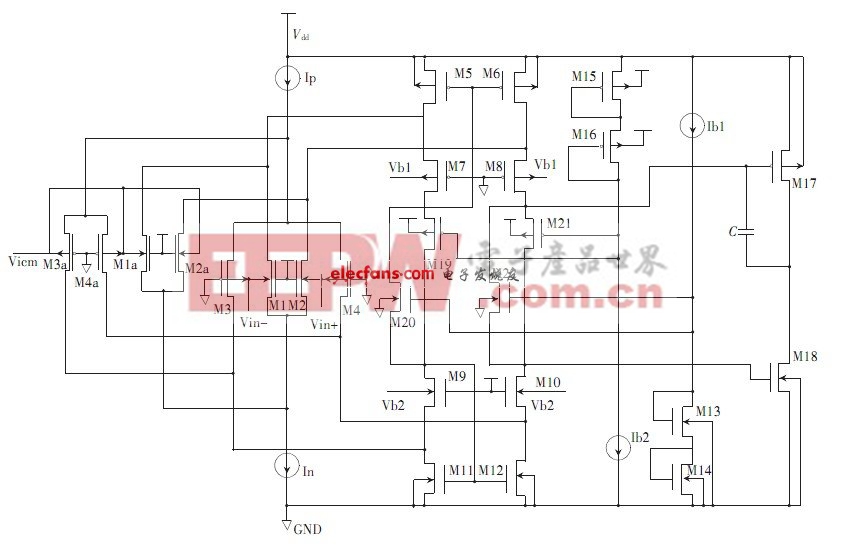

襯底軌至軌運算放大器的實現如圖1所示。

圖1 襯底軌至軌運算放大器

1.1 放大器的輸入級

為使運放的共模輸入在整個電源范圍內變化時電路都能正常工作,采用NMOS和PMOS并聯的互補差分對結構來實現輸入級的軌至軌。如圖1所示,輸入級M1~M4均采用襯底驅動MOSFET。對于柵驅動晶體管來說,輸入級所需要的最小電源電壓為Vsup min=Vgsp+Vgsn+2Vdsat=2Vth+4Vdsat,而襯底驅動差分對所需最小電源電壓為Vsup min=Vsbp+Vbsn+2Vdsat≈Vth+2Vdsat,因此襯底驅動輸入級所需的最小電源電壓要低于傳統差分結構。同時由于襯底驅動MOS管通常工作在耗盡區,其耗盡特性有利于實現低電源電壓下的軌至軌共模輸入范圍。其中,Vgsp、Vgnp分別為PMOS和NMOS管的柵源電壓,Vdsat為MOS管的漏源飽和電壓,Vsbp、Vbsn分別為PMOS管和NMOS管的源襯電壓和襯源電壓,Vth為MOS管的開啟電壓。

典型的軌至軌運算放大器的總跨導在整個共模輸入變化范圍內變化近一倍。跨導的變化帶來增益及單位增益帶寬的變化,也給運算放大器的頻率補償帶來很大困難。為此,本文采用冗余差分對(M1a~M4a)及反折式共源共柵求和電路來控制輸入級跨導以保持恒定。冗余管及求和電路均采用襯底驅動MOSFET,以滿足低工作電壓要求。增加冗余管后的輸入級有一個顯著的優點,即為求和電路提供了恒定的輸出電流,從而有效地消除了輸入級跨導隨輸入電壓變化而對理想頻率補償產生的影響。求和電路采用襯底驅動反折式共源共柵結構以增加共模輸入范圍,提高電源抑制比(PSRR),同時增大電路的差動增益,減小失調,實現低壓下的軌至軌特性。襯底驅動MOSFET的主要缺點是輸入跨導小、輸入電容較大,導致MOSFET的特征頻率fT減小,從而限制了電路的最高工作頻率。因此,襯底驅動輸入級的引入,將不可避免地降低運放的第一級增益(-gmbr0)。本文采用改進型前饋式AB類輸出級以增加有效輸入級跨導,避免襯底驅動技術的缺點。

1.2 放大器的輸出級

在軌至軌運算放大器的設計中,為了充分發揮軌至軌運算放大器的特性,必須設計良好的輸出級。為了達到較高的轉換效率以及輸出全擺幅,軌至軌運算放大器的輸出級通常采用前饋式AB類輸出級。

本設計采用折疊共柵共源作為有源負載,并將其與前饋式AB類輸出級相結合,在提高電壓增益、增加電壓輸出動態范圍的同時,保證了在整個共模輸入電壓范圍內運算放大器的總電壓增益。但是這種傳統結構的缺點是,AB類控制電路的偏置電流源和共源共柵負載成并列關系,從而降低了輸入級的輸

評論