MAXQ構架上閃存和SRAM存儲器的分配

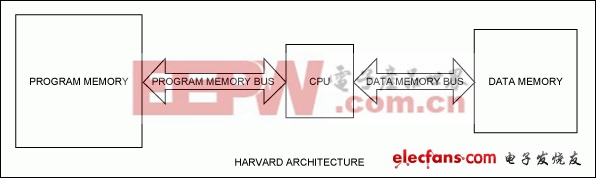

MAXQ架構是一種基于標準Harvard結構、功能強大的單周期RISC微控制器,程序和數據存儲總線相互獨立。這種組織形式要求每個存儲器具有專用總線(圖1),所以可同時讀取指令和操作數。由于不存在單條數據總線的沖突問題,MAXQ指令的執行時間僅需要單個周期。

圖1. Harvard結構

每個MAXQ器件采用以下存儲器類型:

SRAM

固定用途ROM

MAXQ器件也可從閃存、固定用途ROM或SRAM執行程序代碼。從某個存儲器段執行程序代碼時,其它兩個存儲器段可作為數據存儲器(更多詳細信息,請參閱從閃存執行程序和執行固定用途ROM函數部分)。這是因為程序和數據存儲器總線不能同時存取同一存儲器段。

有人可能認為采用Harvard結構的MAXQ微控制器也不能在非易失閃存中儲存數據。然而,MAXQ器件內嵌固定用途ROM函數,允許讀、寫非易失閃存數據。

從閃存執行程序

MAXQ器件中,從閃存執行應用程序時,數據存儲器為SRAM(讀和寫)和固定用途ROM(只讀)。從閃存執行代碼時,數據存儲器映射請參見表1,存儲器映射參見圖2。

SRAM數據存儲器在存儲器映射中位于地址0x0000至0x07FF (字節尋址模式下)或地址0x0000至0x03FF (字尋址模式下)。

固定用途ROM在存儲器映射中位于地址0x8000至0x9FFFh (字節模式)或地址0x8000至0x8FFF (字尋址模式下)。

| 表1. 從閃存執行應用代碼時的數據存儲器映射 | ||||

| Addressing Mode | SRAM | Utility ROM | ||

| Start Address | End Address | Start Address | End Address | |

| Byte Mode | 0x0000 | 0x07FF | 0x8000 | 0x9FFF |

| Word Mode | 0x0000 | 0x03FF | 0x8000 | 0x8FFF |

圖2. 從閃存執行應用代碼時的存儲器映射

執行固定用途ROM函數

執行固定用途ROM函數時,數據存儲器為SRAM(讀和寫)和閃存(讀和寫)。從閃存執行應用程序且變量或數據對象位于閃存時,可通過固定用途ROM函數讀或寫這些變量或數據對象。通過跳轉至執行固定用途ROM函數,即可將閃存作為數據進行存取。從固定用途ROM執行代碼時,數據存儲器映射請參見表2,存儲器映射參見圖3。

SRAM數據存儲器在存儲器映射中位于地址0x0000至0x07FF (字節尋址模式下)或地址0x0000至0x03FF (字尋址模式下)。

字節尋址模式下,CDA0 = 0時,閃存的低半部分在存儲器映射中位于地址0x8000至0xFFFFh;CDA0 = 1時,閃存的高半部分在存儲器映射中位于地址0x8000至0xFFFFh。字尋址模式下,閃存在存儲器映射中位于地址0x8000至0xFFFF。

相關推薦技術專區 |

評論