Leon2處理器IP核技術(一)

Leon2是GaislerResearch公司于2003年研制完成的一款32位、符合IEEE-1754(SPARCVS)結構的處理器IP核。它的前身是歐空局研制的Leon以及ERC32。Leon2的目標主要是權衡性能和價格、高的可靠性、可移植性、可擴展性、軟件兼容性等.其內部硬件資源可裁剪(可配置)、主要面向嵌入式系統,可以用FPGA/CPLD和ASIC等技術實現。

Leon2處理器的片上資源如下:分離的指令和數據Cache、硬件乘法器和除法器、中斷控制器、具有跟蹤緩沖器的調試支持單元(DSU)、2個24位定時器、2個通用異步串口(UART)、低功耗模式、看門狗電路、16位I/O端口、靈活的存儲控制器、以太網MAC和PCI接口。Leon2的VHDL模塊可以在大多數綜合工具上進行綜合,可以在任何符合VHDL-87標準的仿真器上進行仿真;采用AMBA AHB/APB總線結構的用戶設計新模塊,可以很容易加入到Leon2中,完成用戶的定制應用。

為了使Leon2得到國內業界的了解和進一步的應用,本文將從Leon2的結構、技術特點、軟硬件的開發過程和應用實例等四個方面進行介紹。在技術特點中,主要介紹了它所遵循的SPARCV8規范、采用的AMBH2.0內部系統總線協議、容錯設計方法和VHDL編程風格等。

1 Leon2的結構

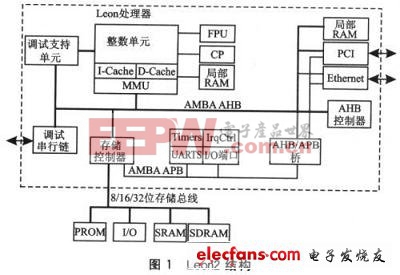

圖1是Leon2的片上結構框圖。整個系統結構由AMBA AHB和APB支撐,連接著SPARC處理器、Cache系統及片上外設等設備。

(1)處理器單元

處理器單元由整數單元IU、浮點單元FPU、協處理器單元CP構成。整數單元的特點有:5級指令流水、分離的數據和指令Cache、支持2~32個寄存器窗口、可選的4個觀察口寄存器、可配置乘法器、可選的16×16位MAC(40位累加器)、基2除法器。可支持的浮點處理器有GaislerResearch的GRFPU,Sun Microsystems的Meiko FPU或其他通用浮點處理單元。Leon2提供了一個通用的用戶可定義的協處理器,同IU并行運行增強了系統功能。

(2)Cache子系統

可配置的模式有直接映射模式和2~4組相聯的多組相聯模式;可選的三種替換算法是LRU、LRR和偽隨機。

(3)片上外設

片上外設包括:2個中斷控制器、2個UART、2個Timer和1個Watchdog、16位的I/O口、存儲器控制器(PROM、SRAM、S13RAM)、PCI橋接器、Ethernet接口、高級片上調試支持單元(DSU)和跟蹤緩沖器等.中斷控制器可以最大處理46個內部和外部中斷。2個串行通信口 (UART),支持8位數據幀、1位校驗位、1位停止位,支持硬件流控功能。調試支持單元(DSU)能夠把處理器設置到調試模式,通過它可以讀寫處理器的所有寄存器和Cache。DSU還包括一個跟蹤緩存,可以保存已執行了的指令和AHB上傳輸的數據。

2 Leon2的技術特點

Leon2的技術特點主要有:采用SPARCV8結構、采用內部AMBA總線結構、容錯設計和VHDL編程風格。

2.1 SPARC V8

SPARC是可擴展處理器體系架構的首字母縮略詞,是一個從RISC派生出的CPU指令集結構(ISA)。指令集結構是指:定義了指令、寄存器、指令和數據存儲器、指令執行對寄存器和存儲器的影響、控制指令執行的算法等內容,但不定義時鐘周期、每條指令的執行時鐘周期數(CPI)、數據通路等內容。作為一個結構,SPARC允許在具有不同性能價格比的廣泛應用中,實現不同系列的芯片和系統,包括科學、工程、編程、實時和商業應用等。SPARC的設計目標是優化編譯器和易于硬件流水線實現。

SPARC處理器由整數單元(IU)、浮點和協處理器單元(FPU和CP)構成。它們各自都有自己的寄存器,其中IU有8個全局寄存器、2~3N個寄存器窗口(由

評論