一種因光纖漂移引起SERDES FIFO溢出的解決方案

摘要

分布式基站系統中,RRU 通常會通過光纖拉遠實現與 BBU 的遠程互聯。由于光纖自身的特性,傳輸過程中必然會引入抖動和漂移;尤其是漂移,因其低頻特性,并且難于濾除,在SERDES 的 FIFO 深度不夠的情況下有可能會造成 FIFO 的溢出。

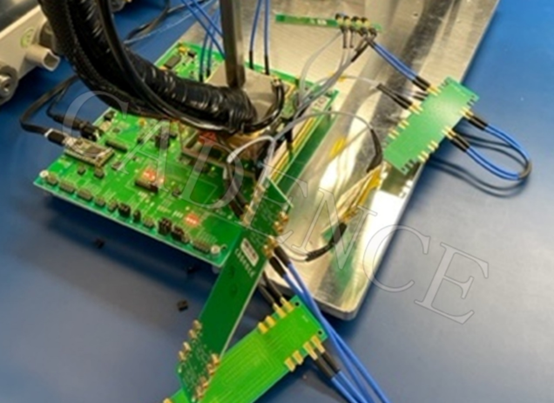

本文首先會對這個問題進行一般性地分析,在此基礎上我們將以德州儀器公司 10G SERDES 器件 TLK10002 為例,提出一個新的解決方案,即采用雙時鐘模式提供 SERDES系統時鐘,并且探討了這種模式的具體實現方式。同時,為了驗證雙時鐘方案的可行性,我們搭建了相應的測試平臺,并給出了相應的測試結果。

1、 光纖漂移引起的 SERDES FIFO 溢出問題分析

1.1 漂移及漂移形成的原因

漂移是一個數字信號的有效瞬時在時間上偏離其理想位置的,非累計性的偏離。所謂的“長期的偏離”是指偏離隨時間較慢的變化,通常認為變化頻率低于 10Hz 就屬于較慢的變化。

實際數字信號存在的相位噪聲,抖動時相位噪聲的高頻成分,漂移是相位噪聲的低頻成分,工程中以10Hz 來劃分高、低頻。產生這兩種頻率成分的機理有所不同。產生低頻成分,也就是產生漂移的主要原因是傳輸媒質和設備中傳輸時延的變化,例如光纖白天受熱變長,時延增加,信號遲到,相位滯后;光纖夜間受冷變短,時延減少,信號早到、相位超前。產生高頻成分,也就是產生抖動的主要原因是內部噪聲引起的信號過零點隨機變化,例如振蕩器輸出信號的相位噪聲,數字邏輯開關時刻的不確定性等。

漂移不會直接導致傳輸產生誤碼,因為傳輸設備的恢復時鐘電路能跟蹤相位的慢變化。漂移幅度變化雖慢,但長期累積幅度可能高達 1000UI[3]。

1.2 漂移引起的 SERDES FIFO 溢出問題分析

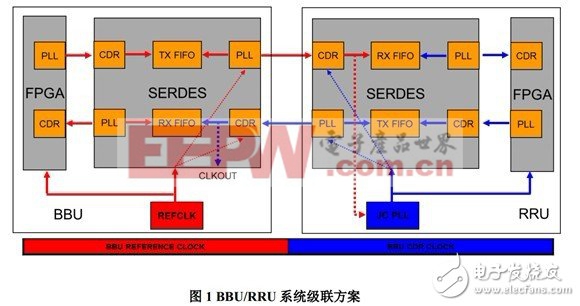

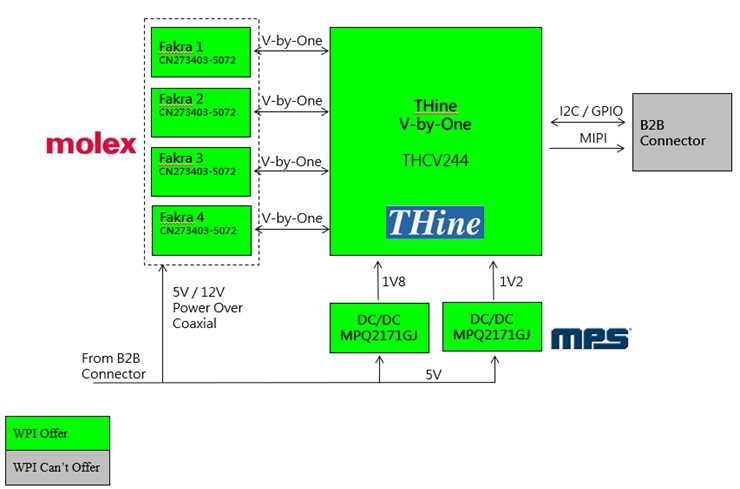

一個典型的 BBU 和 RRU 系統級聯方案如圖 1 所示,在 RRU 一側,由于 JC PLL(主時鐘芯片)會自動跟蹤輸入的串行數據流,當輸入頻率發生變化時,JC PLL 會調整輸出頻率以匹配輸入頻率的變化。在這個跳變瞬間,如果 SERDES 的 FIFO 的讀寫速率可能不一致,導致 FIFO 的沖突,從而造成溢出。但是,通過選擇跳變速度足夠快的 JC PLL,這種溢出是完全可以避免的,而一旦JC PLL 鎖定到輸入數據流,FIFO 讀寫工作在同一速率,就不會存在溢出問題。

在 BBU 一側,值得注意的是時鐘信號的抖動,尤其是漂移引起的 FIFO 溢出。如果這種漂移來自于 BBU 自身的參考時鐘,由于輸入數據數率是與 BBU 速率匹配的,不會造成任何問題; 但是,如上節所闡述的,光纖的溫漂等特性有可能引入新的漂移,如果 RX FIFO 兩側工作在不同的時鐘域, 這種光纖引入漂移會造成 SERDES 內部 FIFO 的碰撞,FIFO 自身的深度如果不足以吸收這種碰撞,就會引起 FIFO 溢出。

2、BBU SERDES 雙系統時鐘方案及具體實現

2.1 TLK10002 內部時鐘架構

TLK10002 是德州儀器公司推出的雙通道 10G SERDES 芯片,它可以支持目前所有的 CPRI 和OBSAI 速率,從 1.2288Gbps 到 9.8304Gbps,因而特別適合無線基站的應用。

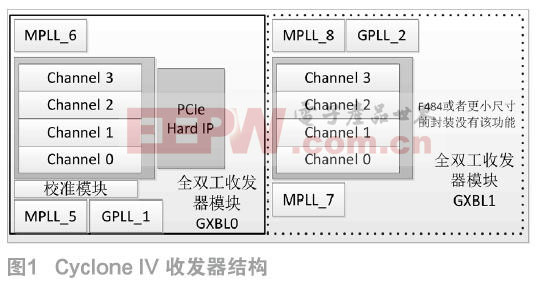

TLK10002 內部的時鐘架構如圖 2 所示,它的 A/B 通道可以通過 REFCLK0P/N 或者REFCLK1P/N 管腳來提供參考時鐘,這兩個參考時鐘的選擇可以通過 MDIO 或者REFCLKA_SEL 和 REFCLKB_SEL 管腳來實現。<

評論