基于HMC704LP4的一種X波段跳頻源設計方案(一)

隨著雷達、電子偵察與對抗、通信等領域技術的發展,對頻率源提出了越來越高的要求,主要表現在高頻率、低相噪、低雜散、小步進、寬頻帶、小體積等方面。頻率合成技術作為系統實現高性能指標的關鍵技術之一,包括四種合成方式:直接模擬式頻率合成、鎖相頻率合成(PLL)、直接數字式頻率合成(DDS)和混合式頻率合成(DDS+PLL)

1 指標要求與方案分析

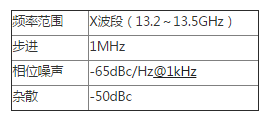

具體指標如下:

頻率范圍:9.87~10.47 GHz

頻率步進:30 MHz

相位噪聲:≤-93 dBc/Hz@1kHz

雜散抑制:≤-60 dBc

跳頻時間:≤50μs

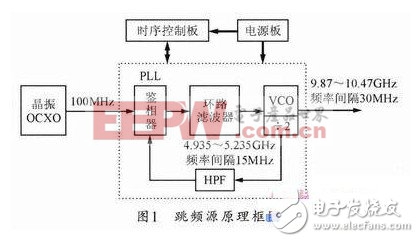

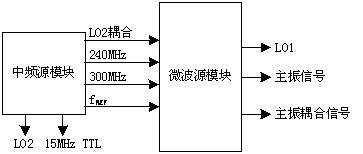

根據所列指標,如果采用直接模擬式雖然相噪、雜散、跳頻時間等指標得以保證,但由于所需設備量大,導致體積大、成本高。DDS+PLL合成方式包括DDS激勵PLL的方式、DDS內插入PLL做分頻器以及DDS與PLL混頻的方式。DDS激勵PLL做分頻器的方式由于DDS最大輸出頻率不高,需要多次倍頻從而惡化相噪,難以滿足系統要求DDS與PLL環外混頻的方式由于輸出信號的帶寬和雜散主要取決于 DDS而難以滿足系統要求,而DDS內插PLL作為分頻器的方式得到的信號雜散較低,頻率分辨率小且能做到較寬的頻帶,但是時鐘頻率較高的DDS價格昂貴。采用鎖相環合成,雜散性能與相位噪聲性能較好,可實現的工作頻帶寬,但頻率切換速度較慢,跳頻時間較長。由于系統并沒有對頻率切換速度提出過高要求,因此從價格方面考慮,我們采用鎖相頻率合成技術,基于低相噪鎖相環芯片HMC704LP4設計該跳頻源。其原理框圖如圖1所示。

選用100MHz OCXO晶振作參考輸入信號,采用Hittite公司的小數分頻數字鎖相環HMC704LP4產生9.87~10.47 GHz、頻率間隔為30 MHz的信號。鎖相環接收來自時序控制板的控制信號,通過對鑒相器的內部寄存器進行控制,產生所需頻點。由于輸出頻率不能被30 MHz整除,如果選擇整數模式則鑒相頻率應為10 MHz,分頻比N較大,噪聲會以20 lgN惡化。因此我們采用小數分頻模式,鑒相頻率為100 MHz,提高了相噪性能,同時由于HMC704LP4采用Delta-sigma調制技術改善了分數雜散性能,使得輸出信號的雜散滿足要求。

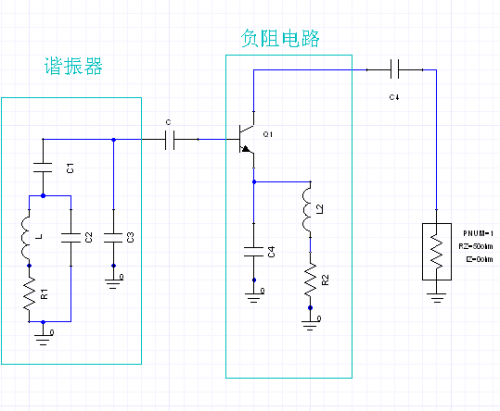

VCO選用Hittite公司的HMC512,頻率范圍為9.6~10.8 GHz,具有二分頻、四分頻輸出,單邊帶相位噪聲為-110 dBc/Hz@100kHz.高通濾波器采用Mini公司的LTCC高通濾波器HFCN-4600+.

2 主要指標分析

2.1 相位噪聲分析

鎖相環系統的相位噪聲來源于參考輸入、反饋分頻1/N、電荷泵和VCO.存環路帶寬內,參考輸入的相位噪聲和N分頻的噪聲占很大比例,電荷泵的相位噪聲也很重要。環路帶寬外的相噪主要由VCO的相噪決定。

根據HMC704LP4手冊,其FOM基底為FP0_dB=-227 dBc/Hz@1Hz;閃爍噪聲基底為Fp1_dB=-266dBc/Hz@1Hz.輸出為10.47 GHz時可得,PLL基底為

X波段跳頻源設計方案(一)" src="http://www.elecfans.com/uploads/131022/1540324-131022104

評論