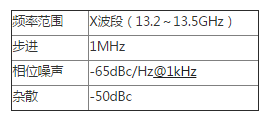

基于HMC704LP4的一種X波段跳頻源設計方案(二)

3 電路設計與實現

3.1 HMC704LP4簡介

HMC704LP4是Hittite公司2011年4月推出的一款低相噪小數分頻鎖相環芯片,其最高工作頻率可達8 GHz,具有整數模式和小數模式,包括鑒相器,精密電荷泵,參考分頻器R,可編程分頻器N,Delta-sigma調制器以及緩沖放大電路等。

其主要性能指標如下:

(1)噪聲基底在整數模式下為-233 dBc/Hz,小數模式下為-230 dBc/Hz;

(2)采用Delta-sigma調制技術改善了分數雜散性能并有周期滑步抑制功能:

(3)最高參考輸入頻率高達350 MHz,在整數模式下鑒相頻率最高為115 MHz,在小數模式下鑒相頻率最高為100 MHz,最小可至DC;

(4)該芯片有八個供電引腳,其中電荷泵部分的供電電壓為5 V,其他供電均為3.3 V;5 V電流典型值6 mA;3.3 V電流典型值52 mA;

(5)三線SPI串口控制。分為HMC模式和開放模式兩種;

(6)體積小:24引腳4×4mm SMT封裝。

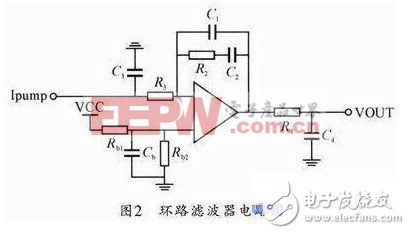

3.2 環路濾波器的設計

環路濾波器設計是鎖相環設計的關鍵部分。環路濾波器處于鑒相器和VCO之間,可以濾除來自晶振的噪聲,鑒相器本身的輸出噪聲和載頻分量,濾除雜散,還可以濾除來自VCO的噪聲,但最重要的是建立起環路的動態特性。

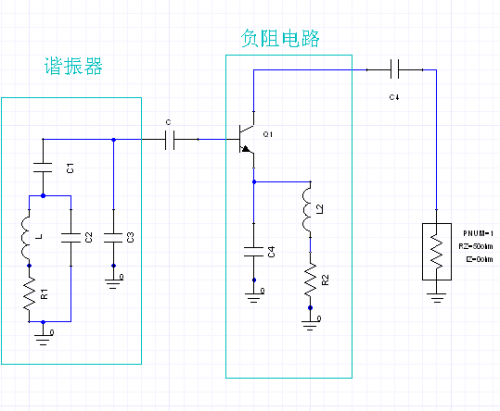

濾波器設計時帶寬需要折中考慮。帶寬小,呵降低近端相噪,環路鎖定時間長。帶寬大,環路鎖定時間短,但會引入參考雜散。本設計借助于Hittite PLL Design設計濾波器。該軟件是Hittite公司推出的鎖相環輔助設計軟件,可以仿真鎖相環的相噪特性、環路特性等。可通過修改環路帶寬、相位裕量、零極點等來修改各參數值。本系統采用四階有源濾波器。電路如圖2所示。

其中Cb=100 nF;Rb1=Rb2=1 kΩ;C1=150 pF;C2=3.3 nF,R2=510 Ω,C3=68 pF;R3=510 Ω,C4=15 pF;R4=1.5 kΩ。此時的環路帶寬280 kHz,相位裕度為60°。

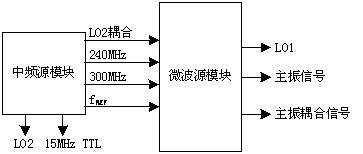

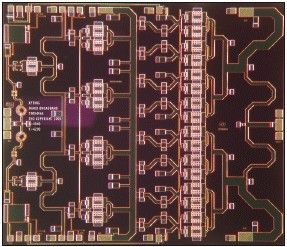

3.3 電路設計與軟件實現

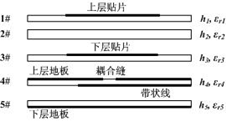

本跳頻源輸出X波段頻率,電路基板采用ROGERS 4350B (介電常數3.48,厚度0.508 mm),各部分電路必須具有良好隔離和屏蔽。整個電路放在鋁腔體中,以保證內部和外部的電磁隔離。腔體分為上下兩層。鎖相環電路放在上層。電源板和控制電路放在下層。為了獲得好的相噪指標,對系統的供電設計要特別注意。系統供電包括+15V、+5 V和+3.3 V.+15 V、+5 V由電源板經過濾波后直接給鎖相環電路供電。+3.3 V由+5 V經LDO產生。各+5 V電源之間用磁珠進行隔離,各+3.3 V電源間也果用磁珠進行隔離。

HMC704寄存器較多,配置起來比較復雜,是設計難點之一。我們采用ALTEra公司的 FPCAEP1C3T14417對HMC704進行配置。通過SPI串口用開放模式配置,可以減少配置

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

分頻器相關文章:分頻器原理 鑒相器相關文章:鑒相器原理 鎖相環相關文章:鎖相環原理

評論