串行RapidIO交換器的應用優勢

EMIF6? 是由 Texas Instruments 開發的一款專利接口,在業內應用多年,反響良好。但是,EMIF6? 現正用于從未嘗試的 DSP 至 DSP 連接等應用。本文闡述了與以相同有效帶寬運行的串行 RapidIO交換器相比,采用 FPGA 的八端口 EMIF6? 交換器具有的優缺點。

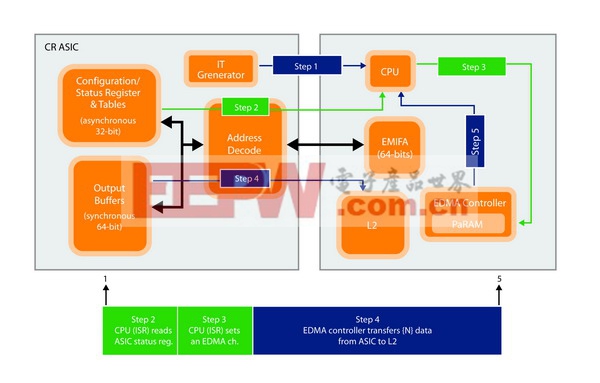

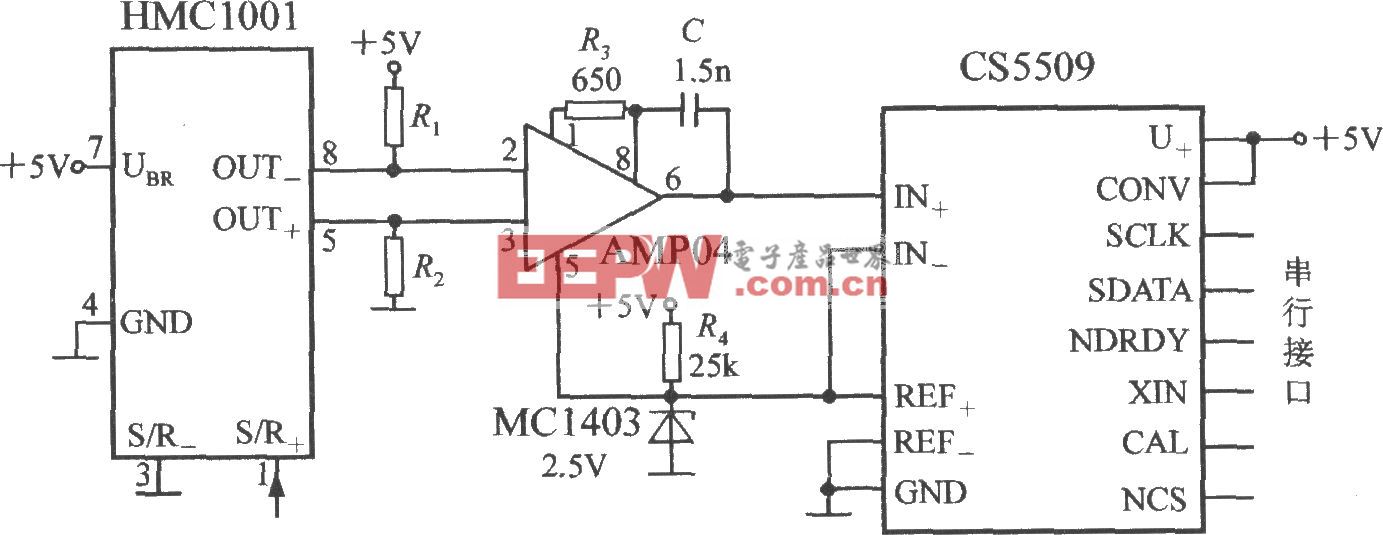

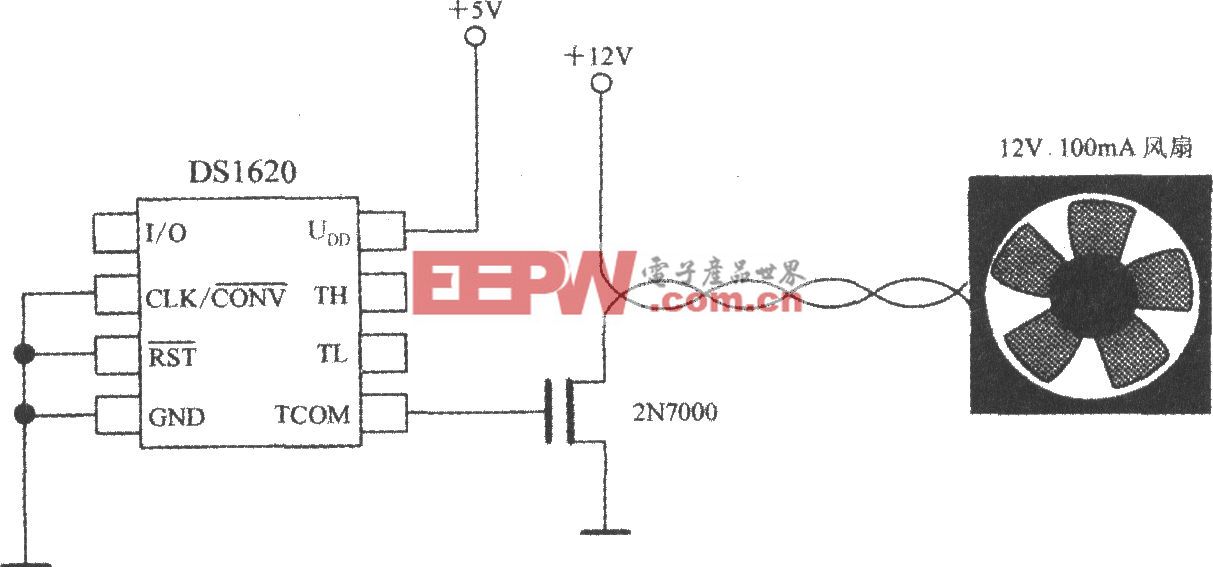

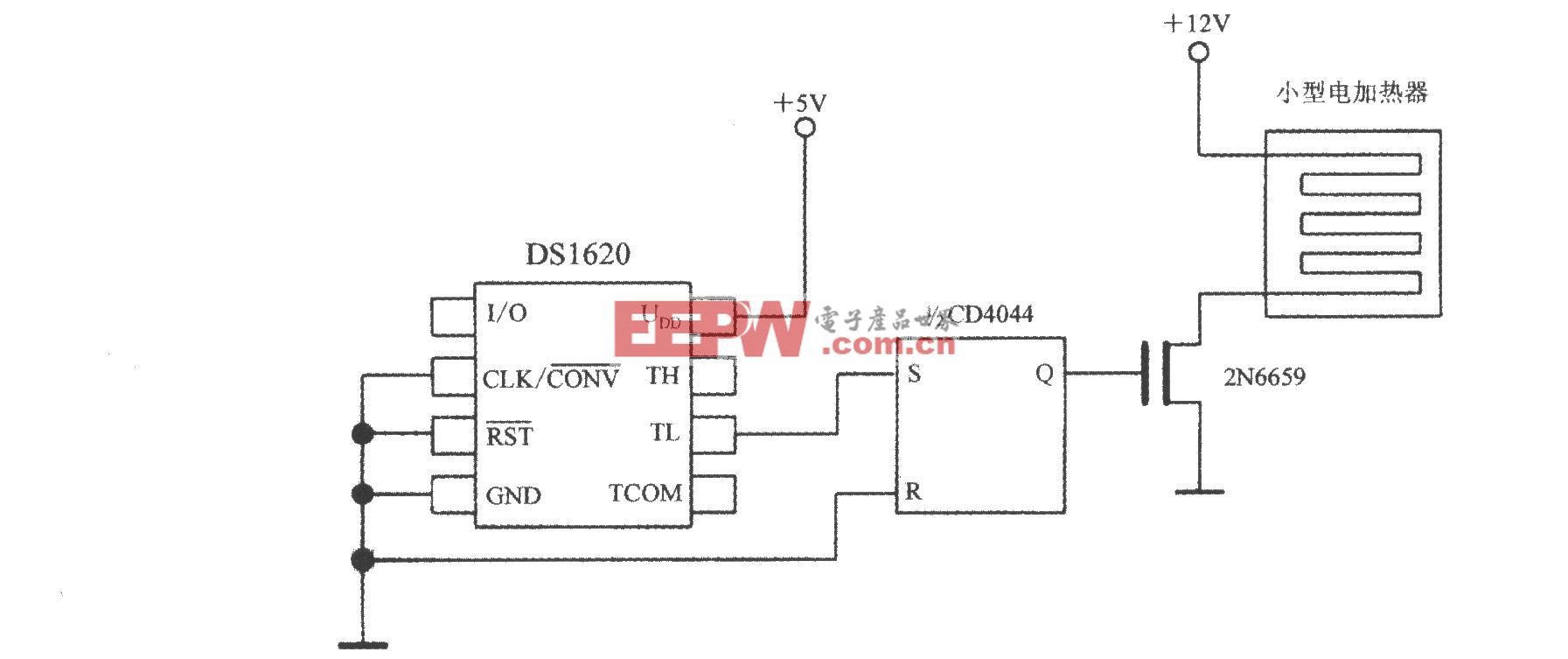

EMIF 標準是一種成熟、穩定的并行外部存儲器接口,且已在許多應用中證明大有益處。但其能力僅限于主機,且需要昂貴的 CPU 中斷服務程序,以便將系統內其他主機的數據傳入設備。支持 EMIF 接口可能還需要龐大的軟件開銷(取決于數據傳輸的大小及頻率)。圖 1 所示的是傳統的EMIF 應用示例,通過CPU 中斷+ EDMA 方法從 CR ASIC 傳至 DSP 的傳輸形式。

通過選擇串行 RapidIO 等先進的系列接口,可實現諸多一般優點:

* 可配置性及性能 – RapidIO以 1.25、2.5 及 3.125Gb的速率支持每個鏈接,且可支持多達八個 4x鏈接或十六個 1x 鏈接。具有確定性及低延時的特點,且提供無阻塞交換矩陣架構。

* 控制 – RapidIO 具有可配置的 CPU 中斷控制、支持錯誤管理及通過性能監控統計支持擁塞控制等特點。它還提供用于硬件錯誤恢復的 CRC 處理。

* 軟件支持 – 納入硬件終止端點從而實現較低的軟件開支。另外,RapidIO 只要求低水平的配置及功能支持,同時提供高度抽象的信息傳遞 API。它還具有 CPU 開銷無需由傳輸數據的大小決定(例如通過少量控制訊息)的優點。

|

|

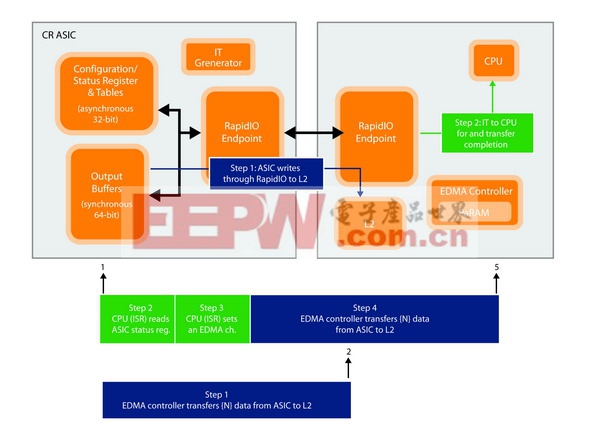

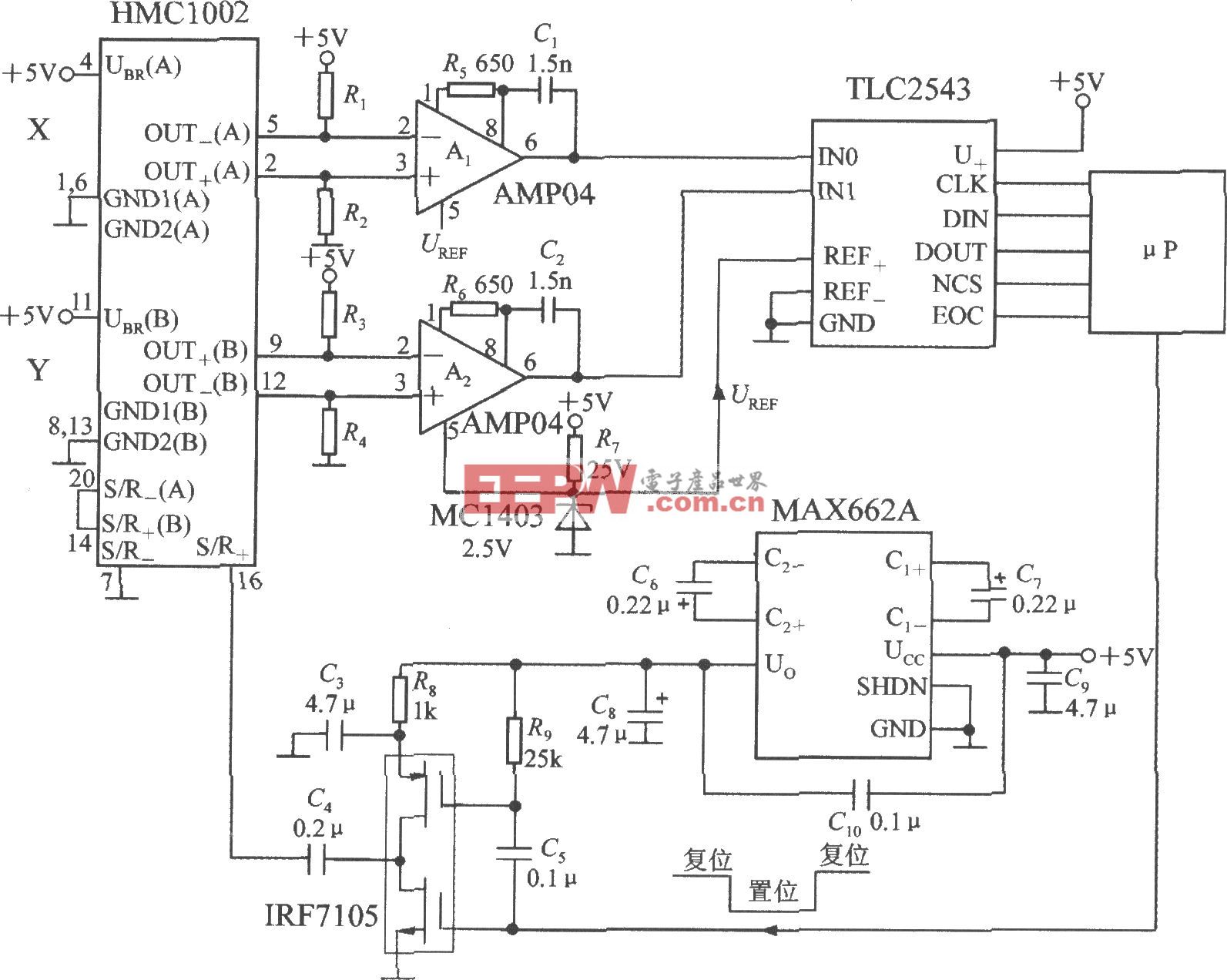

圖2顯示與圖1相同的應用,而在實施時采用串行 RapidIO。采用此方法而不選擇 EMIF6? 的具體優點可概述為以下幾點:

* 靈活性 –EMIF6? 的局限性包括:它不是一個開放式標準接口,且其帶寬限于 8Gb/s 半雙工。另外,它并非可擴展的解決方案。相反,串行 RapidIO 具有開放式標準接口、帶寬可擴展至高達 20Gb/s 及可擴展架構。

* 性能 – EMIF6? 屬于損耗系統,不會存儲和轉發,也不會提供數據的優先次序。另外,通過交換器時還具有不可確定的延時。串行 RapidIO 是無損耗系統,可保證數據包傳送具有四個優先次序等級。通過交換器時具有可確定的延時。

* 開發成本 – 當采用 EMIF6? 接口時,需要 FPGA 設計及確認資源。需承擔的測試平臺費用不可低估,且最后需要持續的產品支持。但是,采用串行 RapidIO,無需進行硅設計,且由于 EMIF6?的相對I/O 要求更高,因此執行本解決方案的成本較低。同時,PCB 的復雜性降低----單個 6? 位 EMIF 接口需要大約 97 只引腳,意味著八個端口的交換器只需要 776 只接口引腳----因此可降低成本。

* 其他優點 – 串行 RapidIO 提供 CRC 處理,可實現基于硬件的錯誤恢復,而EMIF6? 無錯誤檢測/糾正。另外,后者不會提供狀態或確認反饋,而串行 RapidIO 提供錯誤管理及報告功能。此外,較寬的并行接口比串行接口占用更多的 PCB 空間。

兩種解決方案基本相同的一點是功率需求。使用相等的帶寬配置時二者的端點功耗大致相同。當在6?位模式下以133MHz 工作頻率運行時,EMIF 具有 8

評論