用PAC-Designer 設計濾波器

用PAC-Designer 設計濾波器

近年來,數字系統的EDA技術及可編程邏輯器件的發展極大地改變了傳統電子系統的設計思想和實現方法,但是模擬電路的設計手段似乎還停滯不前。現在,由美國Lattice公司推出的模擬電路在系統可編程技術ispPAC使這種情況發生了變化,為模擬電路的設計自動化翻開了新的一頁。

ispPAC 及PAC-Designer的特點

與數字系統的在系統可編程技術類似,模擬電路的在系統可編程技術允許設計者使用開發軟件在計算機中設計和修改模擬電路,并通過編程電纜將設計方案下載到可編程模擬器件中,從而加快設計進程,提高系統設計的準確性,為電子系統設計人員開發產品提供了一條嶄新的途徑。目前由Lattice公司推出的在系統可編程模擬器件有ispPAC10、ispPAC20和ispPAC80三種,這些芯片都是基于E2CMOS編程,支持JTAG編程方式,可編程十萬余次。ispPAC器件的開發軟件為PAC-Designer,采用原理圖輸入方式,并能對設計電路作幅頻特性和相頻特性仿真。

PAC-Designer軟件在濾波器的設計方面獨具特色,其內部集成了不同的宏功能,在宏功能中可以選擇濾波器的類型(如巴特沃斯或賽貝謝夫)和參數(增益、截止頻率、品質因數等)來實現所需的濾波器。

ispPAC10的內部結構

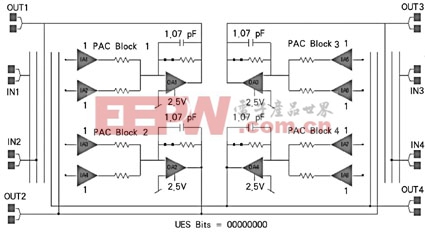

ispPAC10是Lattice公司推出的在系統可編程模擬器件,采用非易失性數字E2CMOS技術,其內部由四個完整的模擬宏單元PACBlock組成,每個PACBlock又由運放、電阻和電容組成,如圖1所示。芯片無需外圍元件就可以靈活實現精密濾波器、求和、求差、增益、衰減和積分等基本模擬功能。用ispPAC10設計電路時,PACBlock中的運放增益可在-10~+10之間進行調節,電容可以在一組固定值之中進行選擇,運放與一系列的反饋電容組合可以產生120種可編程電路,頻率范圍在10kHz至100kHz之間,從而完成不同的電路功能。

用PAC-Designer和ispPAC10設計濾波器

用手工設計二階濾波器時,需要通過理論公式不斷修訂各元件參數,最后才能滿足電路指標的要求,而Pspice和 EWB等軟件一般只能進行模擬仿真,而且仿真實現的電路還必須通過分離元件來完成實際電路。

EWB等軟件一般只能進行模擬仿真,而且仿真實現的電路還必須通過分離元件來完成實際電路。

采用ispPAC10設計帶通或低通濾波器時,不需要任何外部元器件就可以對整個電路的增益、Q值和截止頻率進行調整。通過設定運放增益和電容參數,可以將PACBlock配置成可編程的單極性低通濾波器或積分器,在ispPAC10內部的幾個PACBlock還能夠連接在一起組成更高級數的濾波器。

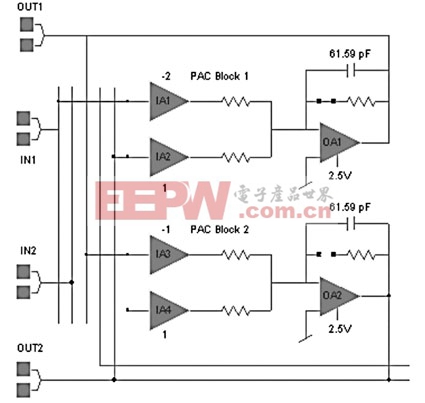

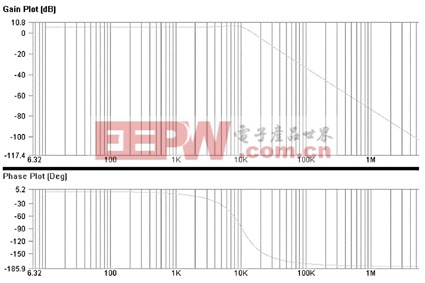

用PAC-Designer宏功能,只要輸入濾波器的參數,系統就會根據設計要求算出反饋電容、電阻及各運放的增益等參數,然后在電路圖編程環境中進行電路布線,修改其參數值。具體過程是,首先打開Tool菜單,選擇Run Macro,彈出如圖2所示的宏功能對話框,選擇“ispPAC10 Bipuad.exe”,在參數輸入對話框中填入F0=2kHz,Q=0.707,DC Gain=2,在Optimize中選擇F0,就可得到截止頻率為2kHz,Q為0.707,增益為2的二階低通濾波器,圖4是濾波器的原理及內部接線圖。保存原理圖,再對其進行幅頻及相頻特性仿真,仿真結果如圖5所示。觀察波形,確認各項參數指標無誤后,最后將設計下載至ispPAC10芯片中。設計方案的下載是通過編程電纜將計算機的并行口和被編程器件連在一起來實現的,接口符合IEEE1149.1JTAG標準。如果目標電路板上有多個可編程器件,需采用菊花鏈的連結方式將幾個器件連在一起。

結束語

在系統可編程模擬器件及設計工具的出現,使模擬電子系統的設計與實現方法發生了很大變化。運用PAC-Designer及ispPAC系列芯片設計濾波器及其他模擬電子線路,將大大縮短產品的開發周期,提高系統的可靠性并減少制造成本,應用前景非常廣闊。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

低通濾波器相關文章:低通濾波器原理

電源濾波器相關文章:電源濾波器原理

數字濾波器相關文章:數字濾波器原理

評論